Reliability Issues and Electrical Characteristics of Rare-earth oxides and their Gate Stacks grown on Germanium Substrates

A Thesis presented By

#### MD. SHAHINUR RAHMAN

To

The Department of Physics

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

in the subject of

Physics

IOANNINA 2009

# « Reliability Issues and Electrical Characteristics of Rareearth oxides and their Gate Stacks grown on Germanium Substrates »

### Ph.D. Dissertation

#### Md. Shahinur Rahman

Department of Physics University of Ioannina, Greece

# **INQUARY COMMISION**

#### 1. E. Evangelou

Assistant Professor, Department of Physics, University of Ioannina (Ph.D. Supervisor & Advisory Committee)

## 2. G. Floudas

Professor, Department of Physics, University of Ioannina (Ph.D. Advisory Committee)

#### 3. A. Dimoulas

Research Director, MBE Lab, NCSR, Demokritos (Ph.D. Advisory Committee)

#### 4. M. Kamaratos

Associate Professor, Department of Physics, University of Ioannina

#### 5. Chr. Kontiras

Associate Professor, Department of Physics, University of Patras

#### 6. N. Konofaos

Assistant Professor, Department of Information & Communication Systems Engineering, University of Agean

#### 7. Pan. Patsalas

Assistant Professor, Dept. of Materials Sciemnce & Engineering, University of Ioannina

# Acknowledgements

I would like to take the opportunity to thank the people that have helped me during my postgraduate studies at the University of Ioannina. This Thesis would not have been possible without the help, guidance and supervision of my advisor Prof. E.K. Evangelou. I would like to thank him for giving me the opportunity to work in his Lab where I have learnt Semiconductor Physics. He was spending hours together with me to solve some scientific questions during my stay in the Lab even in his holidays. In particular, I have learned a lot about reliability characteristics of metal-oxide-semiconductor (MOS) from him and his enthusiasm and supports have made working in his lab a wonderful learning experience and easy.

In addition, I would like to thank Prof. George Floudas and Dr. Thanasis Dimoulas for scientific discussions during our group seminars and for serving as members of the 3-member advisor committee. In particular, I am very much thankful to Dr. Thanasis Dimoulas, who was providing me the samples for my research work.

I would like to thank Prof. Pericles Tsekeris for supporting and helping me in all respects for staying in the University of Ioannina. He taught me Semiconductor Physics, apart from that I was learning Greek culture, a lot about life, and lots more various aspects of life.

I would like to thank Dr. Dimitris Katsanos, Dr. Nikos Konofaos and Dr. Dimitris Anagnostopoulos for their help and cordial encouragement during my research works. Also I would like to thank all members of MBE Lab, DEMOKRITOS for kind cooperation and preparing samples for our Lab.

I am grateful to my colleagues, Iosif Androulidakis, Anthonis Gitsas, Yannis Kyriakidis, Kypros Vassiliou, Mahdy Elmahdy, Kostas Mpoukouvalas, George Papalamparakopulos, Periklis Papadopoulos, and all the graduate students for receiving me as a new graduate student in Department. I have enjoyed a lot interacting with them and their companies.

It's my immense pleasure to thank the Department of Physics, University of Ioannina where I have spent my four years for my doctoral studies. In addition, I would express my deep graduate to our Chairman, Prof. Constantinos Kosmidis for cordial encouragements & help.

I acknowledge Greek State Scholarship Foundation (IKY) for a 4-years fellowship and for giving me the opportunity to complete my PhD study in Greece.

Outside the realm of physics, I would like to acknowledge the support and encouragement of my mother, and my brother and sister, my uncles and all my relatives. I am truly fortunate to have their blessing and good wishes. Their supports and encouragements are the strongest motivation for me to reach this accomplishment.

Especial thanks go to my dear wife, Sultana, for her continuous firm emotional supports and encouragement in all respects.

# ПЕРІЛНЧН

Η παρούσα Διατριβή εξετάζει θέματα αξιοπιστίας και τα ηλεκτρικά χαρακτηριστικά Οξειδίων Σπάνιων Γαιών και αντίστοιχων στοιβών διηλεκτρικών, ανεπτυγμένων πάνω σε υποστρώματα Γερμανίου. Το Γερμάνιο, σε αντικατάσταση του Πυριτίου προσφέρει μεγαλύτερη ευκινησία ηλεκτρονίων (2x) και οπών (4x) στα αντίστοιχα κανάλια τρανζίστορ τύπου MOSFET. Μελλοντικά, η τεχνολογία MOS, με κανάλι Γερμανίου αναμένεται να εφαρμοσθεί σε πλατφόρμες Πυριτίου, λόγω της βελτιωμένης ταχύτητας φορέων. Τα κρίσιμα χαρακτηριστικά επίδοσης των (MOS) πυκνωτών και τρανζίστορ καθορίζονται από τη διεπαφή των υλικών high-κ και του Γερμανίου. Η φτωχή ποιότητα του ενδογενούς οξειδίου (GeO<sub>2</sub>) παρεμπόδισε τη χρήση των υλικών αυτών σε παραγωγή μεγάλης κλίμακας. Τα Οξείδια Σπάνιων Γαιών (REOs) όπως τα CeO<sub>2</sub>, La<sub>2</sub>O<sub>3</sub>, Dy<sub>2</sub>O<sub>3</sub>, Gd<sub>2</sub>O<sub>3</sub> μπορούν να εναποτεθούν άμεσα σε υποστρώματα Γερμανίου. Αλληλεπιδορύν έντονα με το υπόστρωμα, παράγοντας αυθόρμητα (κατά την εναπόθεση) ένα διεπιφανειακό στρώμα το οποίο περιέχει οξειδωμένο Γερμάνιο με βελτιωμένα ηλεκτρικά χαρακτηριστικά. Τα χαρακτηριστικά αξιοπιστίας αυτών των MOS σε υπόστρωμα Γερμανίου έχουν ιδιαίτερη σημασία και αποτελούν το κύριο θέμα της παρούσας διατριβής.

Η παγίδευση φορτίων αποτελεί μείζονα παράγοντα αναφορικά με την αξιοπιστία στις περισσότερες αστάθειες των διατάξεων υλικών high-k. Κατά την υψηλού πεδίου έγχυση σήραγγας ηλεκτρονίων στο στρώμα του οξειδίου, δημιουργούνται στο σύστημα διηλεκτρικού/ημιαγωγού μικροσκοπικά ελαττώματα όπως οι φυσικές παγίδες ηλεκτρονίων, η παγίδευση φορτίου και οι καταστάσεις διεπαφής. Οι φυσικές παγίδες ηλεκτρονίων που δημιουργούνται κατά την καταπόνηση υψηλού πεδίου μπορούν να προκαλέσουν την έγχυση ηλεκτρονίων σε χαμηλές τάσεις, προκαλώντας ρεύμα διαρροής stress-induced leakage current (SILC). Η αυξημένη σημασία του ρεύματος διαρροής stress-induced leakage current (SILC). Το SILC περιγράφεται από μια διαδικασία σήραγγας υποβοηθούμενης από παγίδες

(ΤΑΤ) μέσω των παγίδων οξειδίου που παράγονται από την καταπόνηση. Η πειραματική μέτρηση της ενεργειακής κατανομής των παγίδων αποτελεί κύριο μέλημα προκειμένου να κατανοηθεί ποσοτικά η διαδικασία SILC. Παρά το γεγονός ότι το transient SILC ρεύμα παρέχει χρήσιμες πληροφορίες για την κατανομή των παγίδων οξειδίου, απουσιάζει μια προσεκτική ανάλυση της μεταβατικής διαδικασίας, λαμβάνοντας υπόψη και φαινόμενα σήραγγας ηλεκτρονίων και οπών. Άλλο ένα σημαντικό στοιχείο αποτελούν οι αστάθειες λόγω της συγκέντρωσης φορτίων στη διεπαφή των δυο διηλεκτρικών. Πράγματι, το gate stack bilayer προκαλεί παγίδευση φορτίων, ενώ ορισμένες φορές επιδεικνύει και διηλεκτρική χαλάρωση και το συνδυασμένο αυτό φαινόμενο ονομάζεται Maxwell-Wagner - Instabilities.

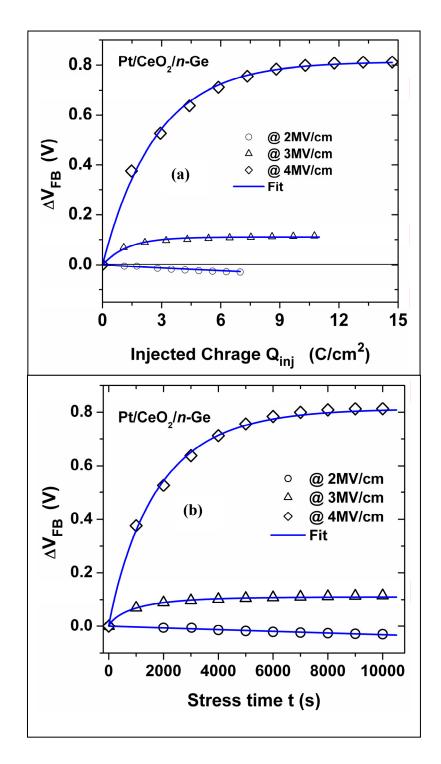

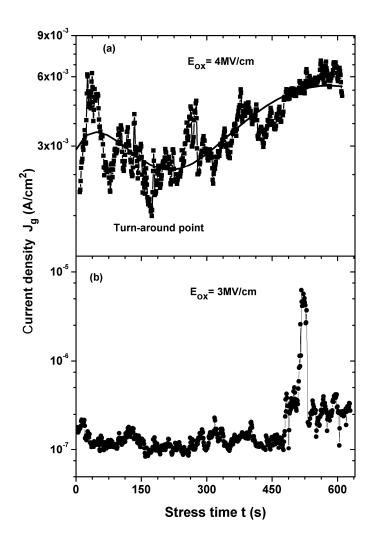

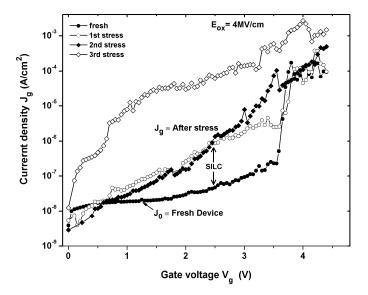

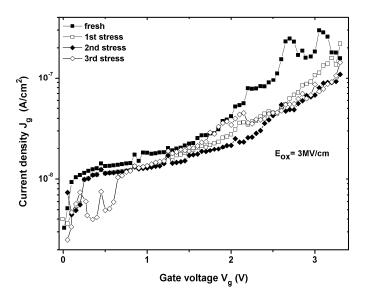

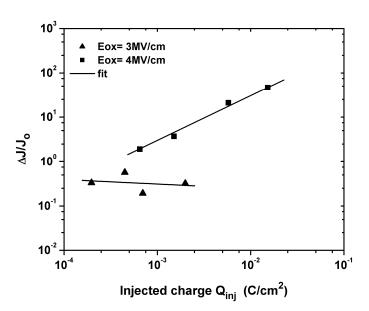

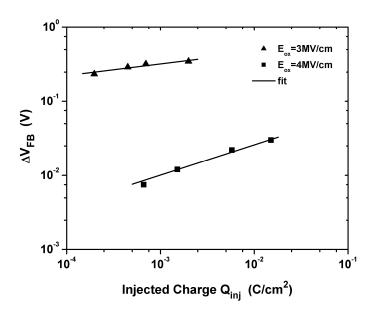

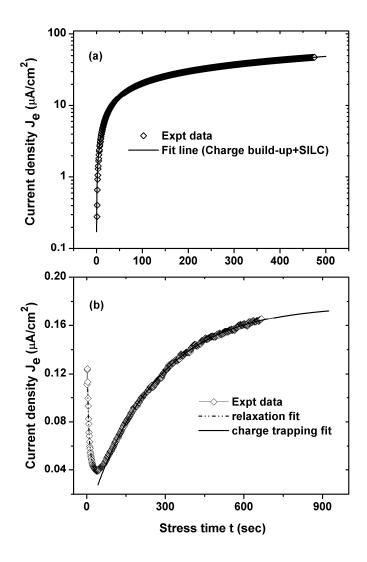

Στο κεφάλαιο 3 ερευνήθηκαν οι επιπτώσεις της παγίδευσης φορέων, του SILC και των συνοριακών παγίδων στο CeO2, εφαρμόζοντας τη μέθοδο "stress and sense". Παρατηρήσαμε ότι τα χαρακτηριστικά παγίδευσης φορτίου και το SILC εμφανίζουν συμπεριφορά εξαρτώμενη από το δυναμικό. Δείξαμε επίσης ότι η παγίδευση φορτίου αποτελεί τον υπερισχύοντα μηχανισμό κατά την καταπόνηση χαμηλού πεδίου ενώ σε υψηλότερα πεδία το SILC επικρατεί έναντι των χαρακτηριστικών της παγίδευσης φορτίων. Η παγίδευση φορτίων και το SILC μαζί μπορούν να εξηγηθούν από το μοντέλο του Nigam, το οποίο αρχικά αναπτύχθηκε για το Si/SiO2. Επίσης αναπτύσσουμε ένα μοντέλο για να εξηγηθούν τα χαρακτηριστικά παγίδευσης φορέων σε διαφορετικής έντασης πεδία καταπόνησης. Στο κεφάλαιο 4 περιγράφονται οι μηχανισμοί μεταφοράς ρεύματος στο CeO2 και παρουσιάζεται πως στα χαμηλά πεδία επικρατεί η εκπομπή Schottky ενώ στα υψηλότερα η μετάδοση Poole-Frenkel.

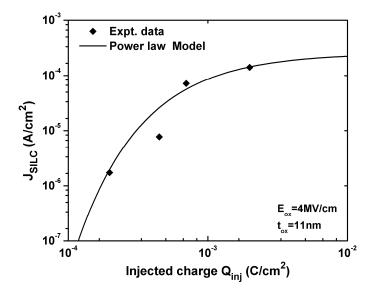

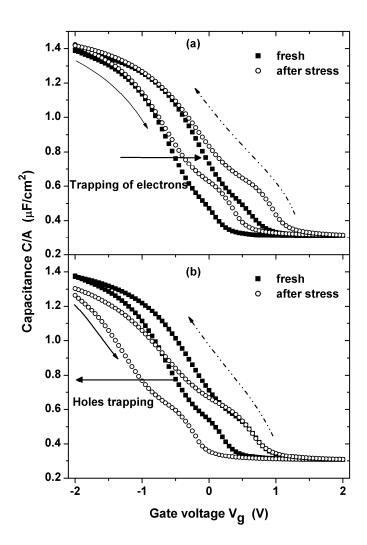

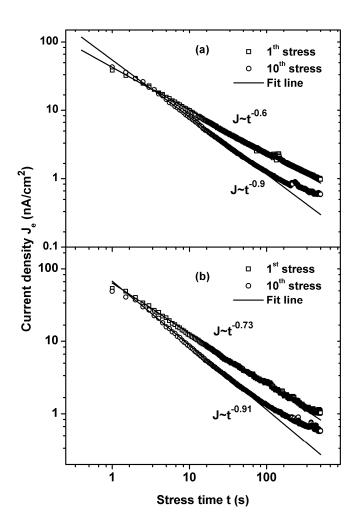

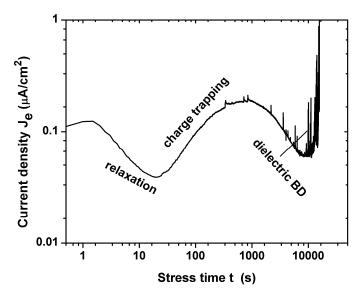

Στα κεφάλαια 5-6, το Stress-induced leakage current (SILC), η παγίδευση φορέων και η διηλεκτρική χαλάρωση εξετάζονται σε Πύλες στοίβας HfO<sub>2</sub>/Dy<sub>2</sub>O<sub>2</sub>. Σε χαμηλά πεδία, το φαινόμενο SILC είναι αμελητέο αλλά σε μεγαλύτερα πεδία ακολουθεί ένα νόμο δύναμης. Σχετικό εύρημα αποτελεί και η αστάθεια Maxwell-Wagner. Το gate stack επέδειξε αρχικά διηλεκτρική χαλάρωση και ακολούθησε παγίδευση φορέων καταλήγοντας σε διηλεκτρική κατάρρευση. Πράγματι, η Πύλη στοίβας είναι η αιτία της παγίδευσης φορτίων.

## **ABSTRACT**

Germanium as a replacement for Silicon in metal-oxide-semiconductor (MOS) devices, offers a higher electron (2x) and hole (4x) mobility than silicon. A Ge channel MOS technology has been expected to be implemented into future high-speed Si platform, because of the enhanced carrier transport. The critical performance characteristics of (MOS) capacitors and transistors are determined by the interface between the high-κ materials and Ge. The poor quality of the native oxide (GeO<sub>2</sub>) however hampered the use of this material in large scale production. One potential solution is the use of Rare-earth oxides (REOs) such as CeO<sub>2</sub>, La<sub>2</sub>O<sub>3</sub>, Dy<sub>2</sub>O<sub>3</sub>, Gd<sub>2</sub>O<sub>3</sub>, which can be directly deposited on Germanium substrates. They form strongly interacting interfaces, producing spontaneously (during deposition) an interfacial layer which contains oxidized Ge with improved electrical characteristics. The reliability characteristics of these MOS devices on Germanium substrates are of important concerns and the main subject of the present work.

Charge trapping is a major reliability concern in most of the high-k material devices. During high field injection of electrons into the oxide layer, microscopic defects like neutral electron traps, and interface states are generated in the dielectric/semiconductor system. The neutral electron traps generated during high field stress can act as a stepping stone for the injected electron at a low voltage, giving rise to a stress-induced leakage current (SILC). The increased importance of the stress-induced leakage current (SILC) in ULSI low-power and non-volatile memory applications has long been recognized. SILC has been described by a process of trap-assisted tunneling through stress generated oxide traps in Si/SiO<sub>2</sub> MOS devices. The experimental measurement of the trap energy distribution represents therefore a primary concern in order to quantitatively understand the SILC process. Although the transient SILC current has been shown to provide useful information about the oxide trap

distribution, a careful analysis of the transient processes, is still lacking. Another important issue is current instabilities due to charge accumulation at the interface of any two dielectrics, that is, gate stack bilayer itself causes charge trapping, sometimes also demonstrate dielectric relaxation, and these combined effects are termed Maxwell-Wagner - Instabilities.

The present work comprises of six (6) chapters, chapter # 1 dealing with the theoretical background and chapter # 2 with the Experimental part. In chapter # 3 the effects of charge trapping, SILC, and border traps in CeO<sub>2</sub> films grown on Ge substrates are investigated, where the subsequent analysis proves that charge trapping characteristics and SILC show voltage dependence behaviour. It is also shown that at low stress field charge trapping is the dominant mechanism while at higher stress field SILC prevails over charge trapping characteristics. Both mechanisms can be explained by a model, which was originally developed for the Si/SiO<sub>2</sub> system. We also develop a model to explain the charge trapping characteristics at different stress fields. In chapter # 4 the current conduction mechanisms in CeO<sub>2</sub> thin films are reported which are governed by Schottky emission at low fields that turn to Poole-Frenkel conduction at higher fields.

In chapter # 5-6 the Stress-induced leakage current (SILC), Charge trapping and Dielectric relaxation effects in HfO<sub>2</sub>/Dy<sub>2</sub>O<sub>2</sub> gate stacks are discussed. At low field the SILC effect is negligible while at higher fields it follows a power law. A pertinent finding from this system is that it shows Maxwell-Wagner instability. The MOS devices show initially dielectric relaxation effects followed by charge trapping that finally reaches dielectric breakdown. As a matter of fact, the gate stack itself is the cause of charge trapping.

# **Table of Contents**

Acknowledgements ΠΕΡΙΛΗΨΗ Abstracts Table of Contents

| Chapter 1-Introduction                                                       |    |

|------------------------------------------------------------------------------|----|

| 1.1-Introduction                                                             | 17 |

| 1.2-High mobility Germanium: possibly a future material for Microelectronics | 21 |

| 1.3-High κ gate dielectrics                                                  | 23 |

| 1.3.1-troduction                                                             |    |

| 1.3.2-Limitation of SiO <sub>2</sub>                                         | 24 |

| 1.3.3-Alternative High-κ dielectrics                                         | 24 |

| 1.4-Using REOs as dielectrics (interfacial passivation layer)                |    |

| 1.5-Metal-Oxide-Semiconductor (MOS)                                          | 33 |

| 1.5.1-Introduction                                                           | 33 |

| 1.5.2-MOS structures                                                         | 34 |

| 1.5.3-Band diagram of an ideal MOS Structure                                 | 35 |

| 1.5.4-Qualitative Description                                                | 36 |

| 1.5.5- Flatband                                                              | 37 |

| 1.5.6- Accumulation                                                          | 37 |

| 1.5.7-Depletion                                                              | 38 |

| 1.5.8-Inversion                                                              | 39 |

| 1.5.9-Surface Space-Charge Region                                            | 39 |

| 1.6-Capacitance-Voltage ( <i>C-V</i> ) characteristic                        | 41 |

| 1.6.1-High–low Capacitance-Voltage ( <i>C-V</i> ) characteristic curves      | 44 |

| 1.6.2-Frequency dispersion of C-V characteristics                            | 45 |

| 1.6.2.1-Frequency dispersion at accumulation                                 | 45 |

| 1.6.2.2-Frequency dispersion at inversion                                    | 46 |

| 1.7-Interface state characterization                                         | 47 |

| 1.7.1-Introduction                                                           | 47 |

| 1.7.2-Extraction of interface trap state density (D <sub>it</sub> )          | 48 |

| 1.7.2.1-Theory                                                               | 48 |

| 1.7.3-Types of Interface tarps                                               |    |

| 1.7.4- $D_{it}$ extraction techniques and conduction method                  | 56 |

| 1.8- Border Traps (N <sub>bt</sub> ) characteristics                         |    |

| 1.9-Current conduction mechanisms in REOs dielectrics                        | 60 |

| 1.10-Reliability Issues                                                      | 61 |

| 1.10.1-Introduction                                                          | 61 |

| 1.10.2-Reliability of MOS                                                    | 62 |

| 1.11-Oxide defects charges                                                   |    |

| 1.11.1-Classification of Oxide defects charges                               |    |

| 1.11.2-Types of defects in MOS devices                                       |    |

| 1.12-Defects generation under electrical stress                              |    |

| 1.13-Dielectric Breakdown                                                    |    |

| 1.13.1-Introduction                                                          | 67 |

| 1.13.2-Types of breakdown                                                    | 68 |

| 1.13.3-Percolation statistical breakdown model                    | 71  |

|-------------------------------------------------------------------|-----|

| 1.14-Oxide Degradation                                            | 73  |

| 1.14.1-Introduction                                               | 73  |

| 1.14.2-Oxide charge trapping characteristics                      | 73  |

| 1.14.2.1-Negative charge trapping –detrapping characteristics     |     |

| 1.14.2.2-Positive charge trapping characteristics                 |     |

| 1.14.3-Stress-induced leakage current (SILC) and neutral traps    |     |

| 1. 15.1-Maxwell-Wagner Instability                                |     |

| 1.15.2-Dielectric relaxation                                      |     |

| 1.16-References                                                   |     |

| Chapter 2-Experimental Details and Characterization Methodologies |     |

| 2.1- Introduction                                                 |     |

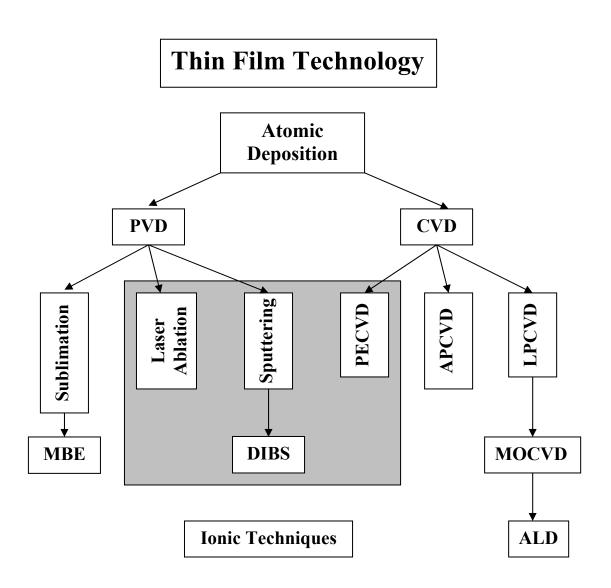

| 2.2- Various deposition techniques                                |     |

| 2.2.1 - Chemical vapor deposition (CVD)                           |     |

|                                                                   |     |

| 2.2.2-Atomic layer deposition (ALD)                               |     |

| 2.2.3Physical vapor deposition (PVD)                              |     |

| 2.2.4-Molecular Beam Epitaxy (MBE)                                |     |

| 2.2.4.1-Advantages of MBE deposition technique                    |     |

| 2.2.5 -Block diagram of thin film deposition techniques           |     |

| 2.3-CMOS processing                                               |     |

| 2.3.1- Introduction                                               |     |

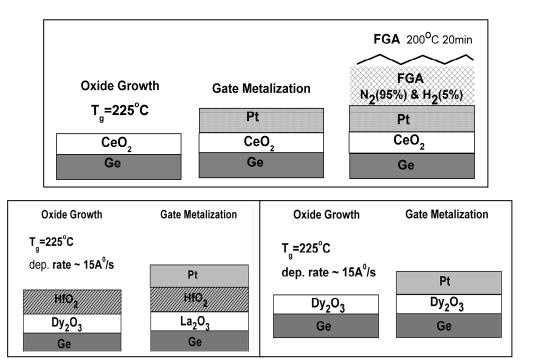

| 2.3.2- Germanium (Ge) Substrates Cleaning and Growth              |     |

| 2.3.3- Outlines of Sample formation and annealing                 |     |

| 2.3.4 – Growth of gate dielectrics                                |     |

| 2.3.5-Metallization (Pt gate electrode)                           | 110 |

| 2.3.6-Forming Gas Annealing (FGA)                                 | 112 |

| 2.3.7 -Back Ohmic Contact                                         | 113 |

| 2.4 -Experimental Techniques and Characterizations                | 113 |

| 2.4.1-Analytical characterizations                                | 113 |

| 2.4.2-X-ray Diffraction (XRD)                                     | 113 |

| 2.4.3- X-ray Reflectivity (XRR)                                   |     |

| 2.4.4 - Transmission Electron Microscopy (TEM)                    |     |

| 2.5 MOS Electrical Characterization and Experimental Setup        |     |

| 2.5.1-Introduction                                                |     |

| 2.5.2 -Capacitance-Voltage ( <i>C-V</i> ) measurements            |     |

| $2.5.3$ - Density of Interface States ( $D_{it}$ )                |     |

| 2.5.4 - Current-Voltage ( <i>I-V</i> ) measurement                |     |

| 2.5.5- Current-time ( <i>I-t</i> ) transient measurement          |     |

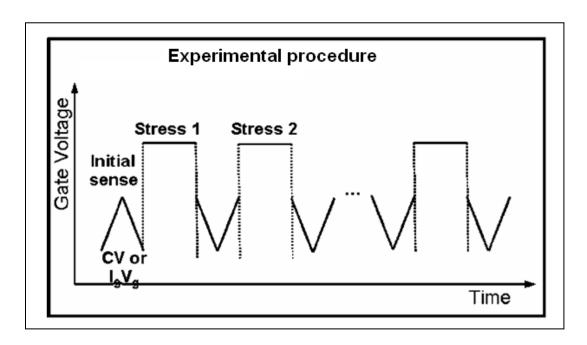

| 2.5.6-Stress and Sense" Characterization Technique                |     |

| 2.6 -Reliability Measurements                                     |     |

| 2.6.1-Introduction                                                |     |

| 2.6.2 -Details of the stress methods                              |     |

|                                                                   |     |

| 2.6.3-Constant Voltage Stress (CVS)                               |     |

| 2.6.4-CVS measurement method                                      |     |

| 2.6.5 -SILC measurement under CVS                                 |     |

| 2.6.6 - Ramp Voltage stress (RVS)                                 |     |

| 2.7 -References                                                   | 133 |

| Chapter 3 - Anomalous Charge Trapping Dynamics, an                                                                                                            |                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| and SILC in Cerium Oxide grown on Germanium substr 3.1-Motivation                                                                                             |                               |

| 3.2-Experimental                                                                                                                                              |                               |

|                                                                                                                                                               |                               |

| A. Anomalous Charge trapping dynamics in CeO <sub>2</sub>                                                                                                     |                               |

| 3.3-Results and Discussion                                                                                                                                    |                               |

| 3.3.1- <i>C-V</i> and <i>I-V</i> measurements                                                                                                                 |                               |

| 3.3.2-Constant Voltage Stress (CVS) measurements                                                                                                              |                               |

| B. Correlation of Charge Build-up and SILC in CeO <sub>2</sub> films .                                                                                        |                               |

| 3.4-Results and discussion                                                                                                                                    |                               |

| 3.4.1-Change of "Border Traps" with Stress                                                                                                                    |                               |

| 3.4.2-CVS at moderate E <sub>ox</sub>                                                                                                                         |                               |

| 3.4.3-CVS at low E <sub>ox</sub>                                                                                                                              |                               |

| 3.4.4-The build-up charges and SILC coefficients                                                                                                              |                               |

| 3.4.5- Capture cross section of traps investigated                                                                                                            |                               |

| 3.5-Summaries                                                                                                                                                 |                               |

| 5.6-References                                                                                                                                                |                               |

| Chapter 4-Current Transport Mechanism in High-к (<br>Grown on Germanium (Ge)                                                                                  | Cerium Oxide Gate Dielectrics |

| 4.1-Motivation                                                                                                                                                |                               |

| 4.2- Introduction                                                                                                                                             |                               |

| 4.3- Experimental                                                                                                                                             |                               |

| 4.4-Results and Discussion                                                                                                                                    |                               |

| 4.5-Conclusions                                                                                                                                               |                               |

| 4.6-References                                                                                                                                                | 181                           |

| Chapter 5-Study of Stress Induced Leakage Current (SI stacks on Germanium (100) 5.1-Motivation                                                                |                               |

|                                                                                                                                                               |                               |

| 5.2-Introduction                                                                                                                                              |                               |

| 5.3-Experimental                                                                                                                                              |                               |

| 5.4-Results and discussion                                                                                                                                    |                               |

| 5.5-Conclusions                                                                                                                                               |                               |

| 5.6-References                                                                                                                                                | 197                           |

| Chapter 6-Investigation of voltage dependent relaxation induced leakage current (SILC) effects in HfO <sub>2</sub> /Dy <sub>2</sub> O <sub>3</sub> substrates |                               |

| 6.1-Motivation                                                                                                                                                | 203                           |

| 6.2-Introduction                                                                                                                                              |                               |

|                                                                                                                                                               |                               |

| 6.3-Experimental                                                                                                                                              |                               |

| 6.4-Results and Discussion                                                                                                                                    |                               |

| 6.5-Conclusions                                                                                                                                               |                               |

| 6.6-References                                                                                                                                                |                               |

| Chapter 7-Conclusions                                                                                                                                         | 215                           |

| Chapter 8-Future Works                                                                                                                                        |                               |

| Curriculum Vitaa                                                                                                                                              | 210                           |

# Chapter-1

#### Introduction

#### 1.1 Introduction

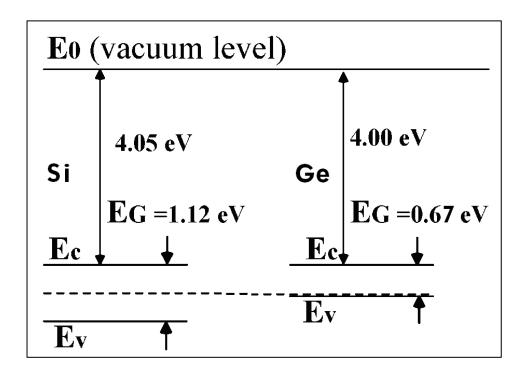

It is well known that compared to Silicon (Si) the use of Germanium (Ge) would bring significant enhancements to low field carrier mobilities for both electrons and holes. Gains up to 2x for electrons and 4x for holes have been reported for bulk germanium [1-4]. Ge is also more compatible than Si with most of the high- $\kappa$  materials that have been proposed for gate insulators. This is because, as opposed to the case of silicon, there is no stable phase of germanium oxide that would form incidentally an additional penalizing layer during the deposition of high-k oxides. One drawback of germanium is related to its smaller optical bandgap ( $E_g \sim 0.67 eV$ ), which raises concerns about junction leakage. For this reason in particular, it is expected that if germanium comes into mainstream CMOS, it will be in the form of GeOI films. This will provide all the benefits of silicon in terms of mechanical properties, weight, cleanliness, and flatness. Beyond CMOS channel mobility improvement that could allow extending Moore's law, Ge is also an enabling solution for combining different functions on the same substrate. Ge can be used directly as an active material for near-infrared photo-detectors.

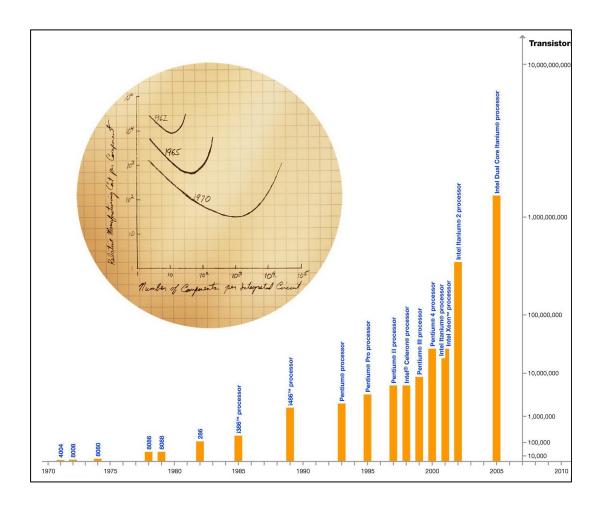

The scaling of MOSFETs has been following the famous Moore's law, which is often stated as the doubling of transistor performance and quadrupling of the number of devices on a chip every three years [5]. This law is shown in Figure 1.1, where the number of MOS transistors integrated in the different generations of Intel's microprocessors is presented as a function of the production year [6].

Figure 1.1: Illustration of Moore's law: number of transistors integrated in the different generations of Intel's microprocessors vs. the production year. After Ref.[6].

Next-generation Intel® Itanium® processors (codenamed Tukwila) take the next big leap in processor-based server technology. As the world's first 2-billion transistor microprocessor since January 2008, Tukwila is designed to provide highly scalable and reliable performance for mission-critical enterprise server solutions [7].

**Figure 1.2:** Comparison between Si and Ge band-diagrams. The valence band edges differ by 0.51 eV. The dashed line shows the mid bandgap level of Si.

As a group IV semiconductor, germanium (Ge) is expected to display many of the same properties as silicon (Si). Yet, despite its better bulk electrical performances (higher hole and low-field mobilities, and narrower bandgap) [8], Ge has not been used much in the past because its oxide is much less stable than SiO<sub>2</sub>. As a result, the electrical properties of the Ge/GeO<sub>x</sub> interface are much worse than for Si/SiO<sub>2</sub>, where *x* is used to emphasize that GeO<sub>2</sub> is not necessarily the dominant oxide form for germanium. The nature of germanium oxide is such that wet chemical procedures for cleaning Ge (so critical for device fabrication) have been very challenging to establish. Yet, with renewed interest for high mobility substrates as Si is reaching some of its fundamental limits, the need to understand and control the passivation of Ge surfaces is even greater.

The success of Si CMOS technology for decades is partly due to the existence of stable oxide and high-quality SiO<sub>2</sub>/Si interface, which is in direct contact with CMOS channel region and permits low defect charge density ( $\sim 10^{10}$  cm<sup>-2</sup>) and interface state density ( $\sim 10^{10}$  cm<sup>-2</sup>eV<sup>-1</sup>), providing high performances of CMOSFET and reliability characteristics. In addition, the recent technological progress in high- $\kappa$  gate dielectric has increased the possibility of high- $\kappa$ /Ge system to be implemented for future gate stack. However, past decade studies on high- $\kappa$ /Ge system indicate that tremendous efforts should be paid on the high- $\kappa$  interface engineering in order to achieve successful scaling of Equivalent Oxide Thickness (EOT) with low-leakage current, good sub-threshold characteristics, high carrier mobility, and acceptable reliability.

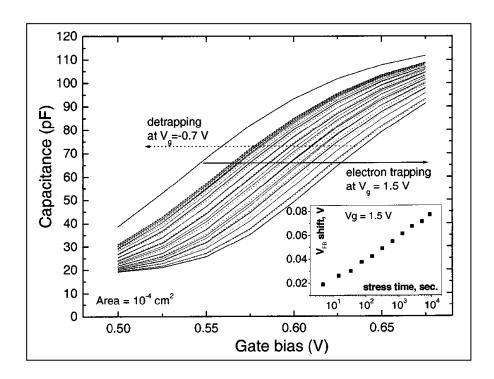

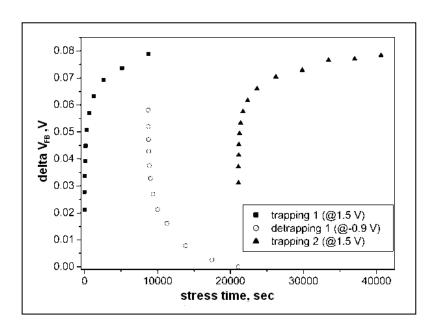

Continued scaling of device dimensions has led to greater emphasis on such issues, and indeed fundamental limits imposed by gate leakage and intrinsic reliability are expected to prevent reduction of the thickness of the high- $\kappa$  gate dielectric in MOS. As a matter of fact, reliability issues, like, charge trapping, stress-induced leakage current (SILC), oxide degradation, dielectric relaxation (DR), as well as, Maxwell-Wagner instability because of bilayer high- $\kappa$  gate stacks itself, are important reliability concerns. Charge trapping causes the threshold voltage to shift with stressing time and is therefore an important transistor reliability issue. SILC is now the limiting factor for down scaling the tunnel oxide thickness in floatinggate based non-volatile memories. A potentially serious device integration problem exists with metal-oxide high- $\kappa$  dielectrics such as HiO<sub>2</sub> and ZrO<sub>2</sub>. Due to DR, the problem is that an applied voltage causes these materials to develop a residual polarization that can remain long after the voltage is removed [9].

## 1.2 High mobility Germanium: possibly a future material for

#### **Microelectronics**

In 1947, the first transistors were fabricated in Bell Labs using bulk germanium as the semiconducting material. For this work its inventors, John Bardeen and Walter Brattain shared the 1956 Nobel Prize in Physics, along with William Shockley. However, by the 1960s its use was largely supplanted with Si due largely to Si's high quality thermal oxide. About a dozen years later, the integrated circuit was independently invented by Jack Kilby, who used Ge substrates, and by Robert Noyce, who used silicon, and for which Kilby received the 2000 Nobel Prize in Physics (Noyce had passed on in 1990). Today, with the 45 nm technology node in production, high- $\kappa$  dielectrics are beginning to replace SiO<sub>2</sub> in the gate, and as such, one of the key reasons for using Si is no longer as relevant. This, combined with performance concerns for Si based devices for and beyond the 22 nm node has made Ge a worthy area for research for high performance devices [10].

In the years since the turn of the millennium, there has been significant progress towards the replacement of the  $SiO_2$  gate dielectric with high dielectric constant (high- $\kappa$ ) materials like  $HfO_2$  and HfSiO(N). With feasible replacements for  $SiO_2$ , the key drawback of Ge, namely the lack of a high quality native oxide, becomes much less significant. This progress in high k R&D, plus the better electron (3900 vs 1400 cm<sup>2</sup>/Vs) and hole (1900 vs 500 cm<sup>2</sup>/Vs) mobilities for Ge over Si has led to a resurgence of interest in Ge [10].

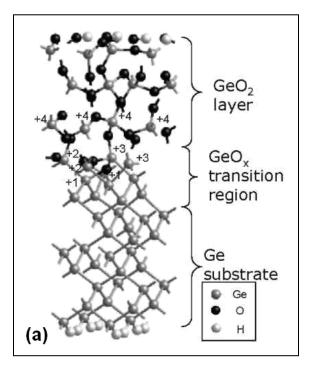

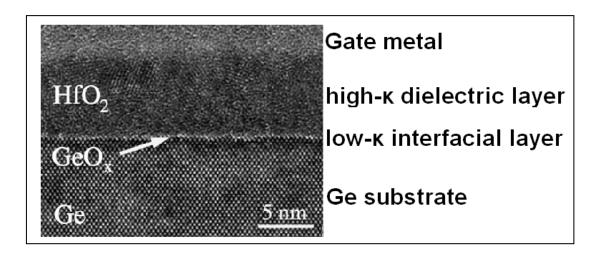

**Fig. 1.3:** (a) Simulated cell for oxidation of Ge to  $GeO_2$  (Ge 4+ oxidation state), with a  $GeO_2$  transition region comprised of Ge in the 1+, 2+ and 3+ oxidation states. (b) Projected Density of States (DOS) for the Ge substrate,  $GeO_x$  transition region, and  $GeO_2$  layer, showing that neither  $GeO_2$  nor  $GeO_x$  states fall within the Ge bandgap. After Ref. [11]

Germanium devices obviously require a substrate for fabrication. The development of effective germanium passivations and gate dielectrics poses a major challenge for germanium

MOS. Density functional theory simulations of a germanium sub-oxide transition region between a Ge substrate and a GeO<sub>2</sub> layer show no states in the Ge bandgap for either the GeOx transition region or the GeO<sub>2</sub> layer, as indicated in Fig. 1.3 (a) and (b). These simulated results suggest that there may be no inherent reason for poor electrical behavior for germanium oxide; rather the poor behavior typically seen could be due to extrinsic effects. For Ge, 2+ and 4+ are the only common oxidation states and GeO and GeO<sub>2</sub> are the only observed bulk oxides [12].

# 1.3 High κ gate dielectrics

#### 1.3.1 Introduction

The dielectric constant ( $\kappa$ ) is a measure of a material's ability to resist the formation of an electrical field within it. Low dielectric constant materials, such as air, show almost no change in orientation of molecules when a voltage is applied. Materials with high dielectric constants polarize their structures to counteract fields they experience. One can model the bonds in these structures as dipoles. As the strength of these dipoles increases, a stronger alignment of the dipoles will be resulted, which often leads to an increased  $\kappa$  value. These aligned dipoles also produce an image charge effect at the dielectric/doped silicon layer interface.

## 1.3.2 Limitation of SiO<sub>2</sub>

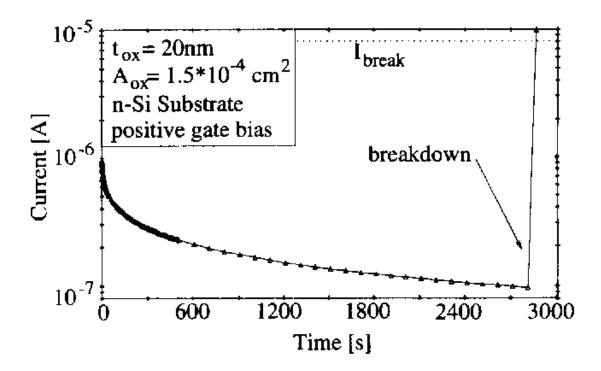

The main problem arising from the scaling of the SiO<sub>2</sub> layer thickness concerns the leakage current flowing through the metal-oxide-semiconductor structure. As a matter of fact, in ultrathin SiO<sub>2</sub> gate layers (thickness typically below 3nm) the charge carriers can flow through the gate dielectrics by a quantum mechanical tunneling mechanisms [13-14]. Another issue related to the thickness scaling concern reliability aspects. During the operation of the MOSFETs in integrated circuit, charge carriers flow through the devices, resulting in the generation of defects in the SiO<sub>2</sub> gate layer and Si/SiO<sub>2</sub> interface [15-16]

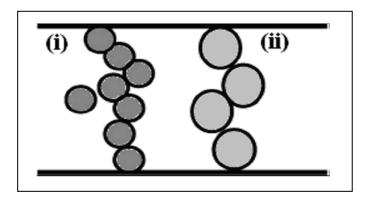

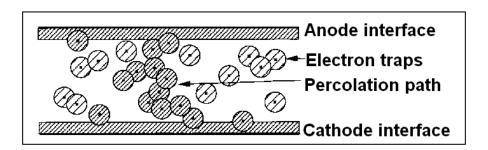

When a critical density of defects is reached, breakdown (or quasi-breakdown) of the gate layer occurs, resulting in the failure of the devices [17-18]. It was shown by Degraeve *et al.* [19] that the time-to-breakdown distributions of the ultrathin SiO<sub>2</sub> layers could be quite well produced by a percolation approach, assuming that breakdown occurred via the formation of a percolation path between defects generated during the electrical stress.

The SiO<sub>2</sub> thickness limit at technological specifications (ITRS) is found to be about 2.2nm at room temperature, and 2.8nm at 150°C. Reliability requirements thus appear even more severe than the leakage current requirements with respect to the scaling of the SiO<sub>2</sub> layer thickness [20].

#### 1.3.3 Alternative High-к dielectrics

From an electrical point of view, the metal oxide semiconductor structure behaves like a parallel plate capacitor: when a gate voltage  $V_g$  is applied to the gate, charges on the metal are compensated by opposite charges in the semiconductor, these latter charges forming the channel connecting the source and the drain of the transistor. The capacitance  $C_{OX}$  of this parallel plate capacitor is given by

$$C_{OX} = \frac{\kappa \varepsilon_0 A}{t_{OX}} \tag{1.1}$$

with  $\kappa$  being the dielectric constant (also referred to as permittivity) of the oxide,  $\varepsilon_0$  being the permittivity of free space (8.85×10<sup>-14</sup> F/cm), A being the capacitor area, and  $t_{OX}$  being the thickness of the oxide.

From equation (1.1) it appears that decreasing  $t_{ox}$  allows us to increase the capacitance of the structure to have low equivalent oxide thickness (EOT), and hence increase in the number of charges in the channel for a fixed value of V<sub>g</sub>. However, as pointed out above, the SiO<sub>2</sub> layer thickness approaches its limits. An alternative way of increasing the capacitance is to use an insulator with a higher relative dielectric constant than SiO<sub>2</sub> (it should be noticed that the relative dielectric constant is also represented by the letter  $\kappa$  and one speaks about high- $\kappa$  materials). One could then use a thicker gate layer and, hopefully, reduce the leakage current flowing through the structure and also improve the reliability of the gate dielectric. The equivalent oxide thickness (EOT) of a material is defined as the thickness of the SiO<sub>2</sub> layer that would be required to achieve the same capacitance density as the high-κ material in

consideration. According to equation (1.1), is thus given by

$$\frac{EOT}{\varepsilon_{r,SiO_2}} = \frac{t_{high-\kappa}}{\varepsilon_{r,high-\kappa}}$$

$$EOT = \frac{\varepsilon_{r,SiO_2}}{\varepsilon_{r,high-\kappa}} t_{high-\kappa}$$

(1.2)

where  $t_{high-\kappa}$  and  $\varepsilon_{r,high-\kappa}$  are the thickness and relative dielectric constant of the high- $\kappa$  material, respectively. As an example, using  $ZrO_2$  as gate dielectric ( $\kappa = 20$ ) would allow us to use a 5.1 nm thick layer in order to achieve a capacitance equivalent to a 1 nm thick SiO<sub>2</sub> layer; the equivalent oxide thickness of this ZrO<sub>2</sub> layer is thus 1 nm.

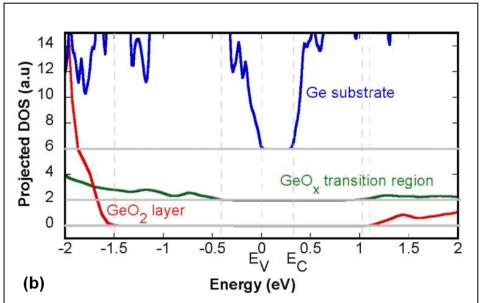

Actually, when a high- $\kappa$  metal oxide like ZrO<sub>2</sub> or HfO<sub>2</sub> is deposited on a Ge substrate, an ultrathin low- $\kappa$  interfacial layer, either GeO<sub>x</sub> or GeM<sub>y</sub>O<sub>x</sub>, (where M is Zr or Hf) forms at the Germanium interface, as illustrated in Fig. 1.4. This interfacial layer may

**Fig. 1.4:** Schematic illustration of MOS structure with a high-κ gate stack, formed by a low – κ interfacial layer and a high-κ dielectric layer. After Ref. [21]

grow either during the deposition of the high- $\kappa$  dielectric or during post-deposition anneal processes. It should be noticed that another low- $\kappa$  layer can also form at the high- $\kappa$  dielectric/metal gate interface.

The capacitance of the gate stack,  $C_{tot}$  then results from the combination in series of the low- $\kappa$  (l- $\kappa$ ) and high- $\kappa$  (h- $\kappa$ ) dielectric layer capacitances, i.e.

$$\frac{1}{C_{tot}} = \frac{1}{C_{low-\kappa}} + \frac{1}{C_{high-\kappa}} \tag{1.3}$$

The equivalent oxide thickness then reads

$$EOT = \frac{\varepsilon_{r,SiO_2}}{\varepsilon_{r,l-\kappa}} t_{h-\kappa} + \frac{\varepsilon_{r,SiO_2}}{\varepsilon_{r,h-\kappa}} t_{h-\kappa}$$

$$EOT = EOT_{low-\kappa} + EOT_{high-\kappa}$$

$$EOT = t_{int} + EOT_{high-\kappa}, \qquad (1.4)$$

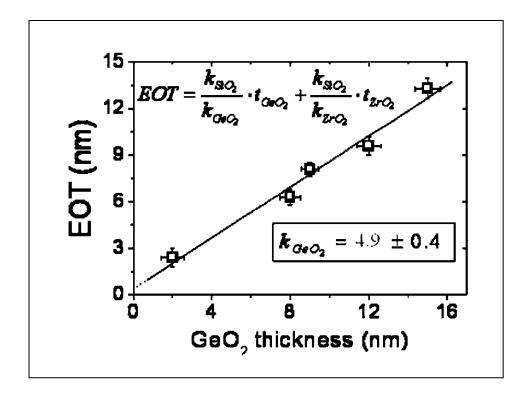

the presence of the low- $\kappa$  interfacial layer increases the equivalent oxide thickness of the gate stacks (Fig.1.5), and should be as thin as possible to achieve the equivalent oxide thickness (EOT) required by the ITRS.

**Fig. 1.5:** EOT as a function of  $t_{ox}$  for samples with  $2nmZrO_2/GeO_2/n$ -Ge structures. The  $\kappa$ -value of  $GeO_2$  is found around  $\sim 4.9$  and  $\kappa$ -value for  $ZrO_2$  (tetragonal phase) around 44. After Ref. [22].

A lot of effort focused on the investigation of high- $\kappa$  gate dielectrics, for the potential replacements of SiO<sub>2</sub> in advanced CMOS technologies. A list of materials studied in the literature is given in *Table 1.1* together with their relative dielectric constants.

Table 1.1: Examples of high-к materials studied in the literature for the potential replacement of SiO<sub>2</sub> as advanced gate dielectrics. After Ref. [20].

| Material                       | Dielectric constant ε <sub>r</sub> | Energy gap<br>E <sub>g</sub> (eV) | Material                       | Dielectric constant ε <sub>r</sub> | Energy<br>gap<br>E <sub>g</sub> (eV) |

|--------------------------------|------------------------------------|-----------------------------------|--------------------------------|------------------------------------|--------------------------------------|

| $Al_2O_3$                      | 9-11                               | 8.7                               | Dy <sub>2</sub> O <sub>3</sub> | 11-14                              | -                                    |

| Ta <sub>2</sub> O <sub>5</sub> | 25-26                              | 4.4                               | Nb <sub>2</sub> O <sub>5</sub> | 11-14                              | -                                    |

| TiO <sub>2</sub>               | 50-80                              | 3.05                              | Gd <sub>2</sub> O <sub>3</sub> | 9-14                               | 5.9 <sup>b</sup>                     |

| CeO <sub>2</sub>               | 21-50                              | 3.3 <sup>a</sup>                  | SrTiO₄                         | 50                                 | 5.2                                  |

| SrTiO <sub>3</sub>             | 200                                | 3.2                               | ZrO <sub>2</sub>               | 14-25,44 <sup>a</sup>              | 5.8                                  |

| Y <sub>2</sub> O <sub>3</sub>  | 12-18                              | 6.0                               | Si <sub>3</sub> N <sub>4</sub> | 7.4                                | 5.1                                  |

| HfO <sub>2</sub>               | 15-25                              | 5.6                               | La <sub>2</sub> O <sub>3</sub> | 21-30                              | 5.7                                  |

<sup>&</sup>lt;sup>a</sup>After Ref. [22] <sup>b</sup> After Ref. [23]

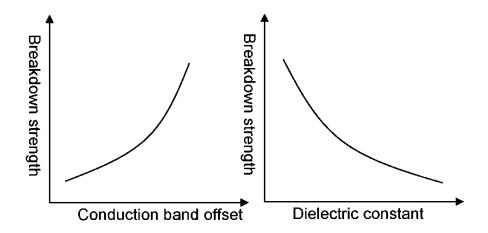

Since SiO<sub>2</sub> approached its physical limit, alternative dielectrics have been introduced, which meet stringent requirements including thermal stability, large band gap, and compatibility to conventional CMOS process. Moderate dielectric constant ( $\kappa$ ) materials (15~30) were preferred due to fringing field induced barrier lowering. It was reported that a universal relation between  $\kappa$  value and breakdown properties. In general, as  $\kappa$  increases, barrier height and breakdown strength decreases (Fig.1.6). A material structure plays an important role of breakdown of the high- $\kappa$  dielectrics. In addition, different charge fluence by different barrier height changes breakdown properties as well.

Fig. 1.6: A universal relation between band offset and breakdown strength.

## 1.4 Using REOs as dielectrics (interfacial passivation layer)

High mobility Germanium metal oxide field effect transistors with high- $\kappa$  gates are considered to be good candidates for high performance applications. To develop a viable Ge MOS technology, the main challenge is to have better Ge surface passivation methodology and identify appropriate high-k gate dielectrics to combine oxide scaling below 1 nm with good electrical quality of the interfaces as well as reliability aspects.

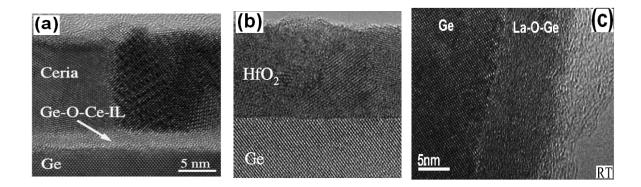

High- $\kappa$  dielectrics, for example, HfO<sub>2</sub> deposited directly on Ge gives sharp interfaces (1.7 (b)) [21] however the electrical behavior is very poor. One of the solutions could be the use of the dielectric together with an interfacial layer (IL) to form gate stack. The gate stack must combine good potential for scaling with good device performance characteristics which is perhaps the most challenging issue in Ge technology. Different efforts have been demonstrated as a passivation interfacial layer, such as, GeON [24], GeO<sub>2</sub> [25] to form gate stacks on Ge surface. It has also been demonstrated on the basis of MOS capacitors that HfO<sub>2</sub>, ZrO<sub>2</sub> with these IL are thermally stable [26-27] and have good potential for scaling giving equivalent oxide thickness (EOT) well below 1 nm [28-29] and  $J_g$  below 1 A/cm<sup>2</sup> the latter being several orders of magnitude lower than that of HfO<sub>2</sub>/Si and SiO<sub>2</sub>/Si systems.

An alternative approach to the passivation problem could be the use of rare earth oxides [30] A number of these oxides such as La<sub>2</sub>O<sub>3</sub>, CeO<sub>2</sub>, Gd<sub>2</sub>O<sub>3</sub>, Dy<sub>2</sub>O<sub>3</sub> can be deposited directly on Ge with improved electrical characteristics, i.e., these oxides are friendly with Ge producing well behaving device characteristics, especially in metal-insulator- semiconductor (MIS) capacitors, and giving good passivation characteristics. A possible reason for this behavior is that rare earth oxides react strongly with the substrate resulting in catalytic oxidation of Ge and in the spontaneous formation of stable interfacial layers.

In the case of CeO<sub>2</sub>, a significant reduction of  $D_{it}$  in the  $10^{11} \text{eV}^{-1} \text{cm}^{-2}$  range is observed. This is a substantial improvement with respect to MBD-prepared HfO<sub>2</sub>/GeON gates. On the other hand, CeO<sub>2</sub> suffers from leakage since it has a low band gap of about 3.3 eV [23]. In addition, an interfacial layer (IL) is spontaneously formed [Fig. 1.7(a)] increasing with film thickness and deposition temperature [21] which makes gate scaling difficult. Despite of that, MIS capacitors suffer from high leakage [31] due to the low energy gap of CeO<sub>2</sub> raising concerns about its scalability to low equivalent oxide thickness (EOT) values. Gd<sub>2</sub>O<sub>3</sub> has attracted interest mainly because it can be grown in crystalline form on Ge with abrupt interfaces [32]. However, there is not enough evidence at the moment about its dielectric quality and its suitability as a gate dielectric for Ge devices. For the case of La<sub>2</sub>O<sub>3</sub>, Ge diffuses in the oxide film most probably resulting in intermixing of La–O [Fig. 1.7(c)] with the substrate [33]. At the same time,  $D_2O_3$  shows good passivation properties when deposited on Ge substrates [34-35]. Using CeO<sub>2</sub>, La<sub>2</sub>O<sub>3</sub>, or Dy<sub>2</sub>O<sub>3</sub> as ultrathin passivating layer and combining it with HfO<sub>2</sub> cap, leakage is improved resulting in long channel functional p- and n-FETs, reduce the interface defect-assisted generation of minority carriers, and also improve electrical characteristics [33-36].

It has been drawn more attention, in particular, on the properties of artificially and spontaneously formed interfacial layers [21]. Two types of interfaces had been examined.

The first is a non-reacting one made by direct deposition of HfO<sub>2</sub> on Ge by MBD. The main characteristics are atomically sharp interface with no sign of oxidized Ge as inferred from XPS and negligible Ge diffusion in the HfO<sub>2</sub> when the deposition temperature is kept sufficiently low. However, samples with abrupt interfaces give poor electrical (C-V and I-V)characteristics. The C-V characteristics can be partly recovered by artificial formation of a thin GeON passivating layer [2-3], despite the fact that this layer is unstable in contact with overlaying HfO<sub>2</sub>, and after dissociating (at least in part) allows Ge to diffuse in the HfO<sub>2</sub>. Although GeON interfacial layers are beneficial [24], C-V and G-V characteristics remain far from ideal exhibiting large hysteresis, strong frequency dispersion, particularly in inversion, and high density of interface states  $D_{it}$ . The second type of interfaces examined is a strongly reacting interface between the rare earth CeO<sub>2</sub> and Ge, producing spontaneously (during deposition) an interfacial layer which contains oxidized Ge [4]. In contrast to GeON/HfO2, the interfacial layer in the CeO<sub>2</sub>/Ge system is stable showing limited Ge diffusion in HfO<sub>2</sub> when the deposition temperature is kept sufficiently low [21]. CeO<sub>2</sub>/Ge metal insulator semiconductor capacitors show improved C-V characteristics compared to GeON/ HfO<sub>2</sub> with very small frequency dispersion, much reduced hysteresis and  $D_{it}$  around  $1\times10^{12}~{\rm eV}^{-1}~{\rm cm}^{-2}$ [4]. Several other rare earth oxides (La<sub>2</sub>O<sub>3</sub>, Dy<sub>2</sub>O<sub>3</sub> and Gd<sub>2</sub>O<sub>3</sub>) can be deposited directly on Ge without an artificially made interfacial layer and this also shows improved electrical behavior.

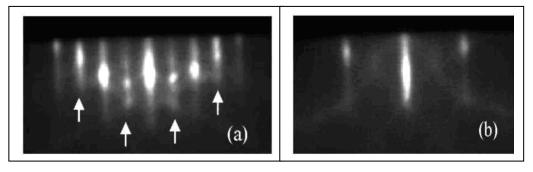

Fig. 1.7: Cross-sectional TEM micrograph showing (a) ceria(CeO<sub>2</sub>) dielectric (b) HfO<sub>2</sub>, and (c) La<sub>2</sub>O<sub>3</sub> deposited directly on a clean Ge surface at a temperature Td=225°C (a)-(b) and (c) at room temperature. The brighter contrast shows the interfacial layer (see (a)) which is formed spontaneously during the deposition of ceria, while for HfO2 is non-reacting interface (see (b)), while in (c) spontaneous formation of germanate (La-O-Ge). (a) & (b) After Ref. [33], (c) After Ref. [37].

Suffering from high leakage current or low effective dielectric constant, these oxides cannot stand alone as gate dielectrics; however they could play the role of an efficient passivating layer in more complex gate stacks for future Ge devices. As a final concluding remark, we note that avoiding oxidation of Ge does not guarantee better passivated interfaces with improved electrical behavior. This is proven by the fact that interfaces free of oxidized Ge (such as those formed by direct deposition of HfO<sub>2</sub>/Ge) show poor electrical behavior. In addition, the CeO<sub>2</sub>/Ge system with a thick interface containing oxidized Ge shows significantly improved characteristics. Instead of trying to avoid Ge oxidation altogether, we should rather avoid germanium oxides in the wrong oxidation states. On the other hand, germanium oxide in the right oxidation state (either 2+ or 3+ according to XPS results [21] may provide a desirable passivating layer. This could be formed by identifying the right material to oxidize Ge perhaps through a catalytic reaction as in the case of ceria. This could lead to a new approach.

## 1.5 Metal-Oxide-Semiconductor (MOS)

#### 1.5.1 Introduction

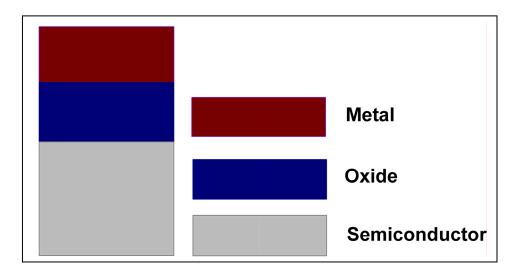

As the semiconductor industry strives for smaller and faster devices, many issues need to be addressed in order to reach targeted objectives. One major issue is the scaling of device dimensions. As lengths and widths reduce, film heights (thickness) must also reduce. One of these areas is the gate dielectric in a Metal-Oxide-Semiconductor (MOS) structure. The gate dielectric thickness is the smallest fabricated dimension in MOS transistors today. Electrical characterization of the MOS test structures is crucial in the development of future MOS devices and circuitry. The Metal-Oxide-Semiconductor (MOS) structure plays a significant role in MOS Field Effect Transistors (MOS FETs) which are prevalent in the integrated circuit technology of today. The MOS capacitor is the metal-insulator-semiconductor structure that creates the conductive channel in a MOSFET. With the use of semiconductor processing equipment, these structures can be fabricated together to form a parallel plate capacitor as shown in Fig. 1.8 where the metal gate and the semiconductor substrate form the metal plates and the insulator forms the dielectric between the two plates. These structures are used extensively in research as a process control that addresses the need for characterization of ultra-thin oxides and alternative gate dielectrics.

#### 1.5.2 MOS structures

To do this research, a fundamental understanding of MOS materials is vital. One useful tool is the semiconductor band structure of these materials. Figure 1.8 shows the ideal case of the MOS structure. In the ideal case, several assumptions have been made [38]: (i) there are no charges present in the dielectric film; (ii) the dielectric is a perfect insulator where no current can pass through under different biasing conditions; (iii) the semiconductor thickness must be large enough to contain a field free region in the bulk of the substrate despite the applied gate potential; (iv) the semiconductor is a uniformly doped substrate; and (v) the backside semiconductor-metal contact must be ohmic.

Fig. 1.8: A MOS capacitor where the wine color shaded portion represents the metal electrode, the "navy blue" portion represents the insulating dielectric, and the light gray shaded portion represents the Germanium substrate. This forms a parallel plate capacitor.

#### 1.5.3 Band diagram of an ideal MOS Structure

Now that the assumptions have been given, static biasing issues can be addressed for metal serving as the gate electrode of the MOS capacitor. The four static biasing conditions that will be addressed are: accumulation, flatband, depletion (in the substrate), and inversion (in the substrate).

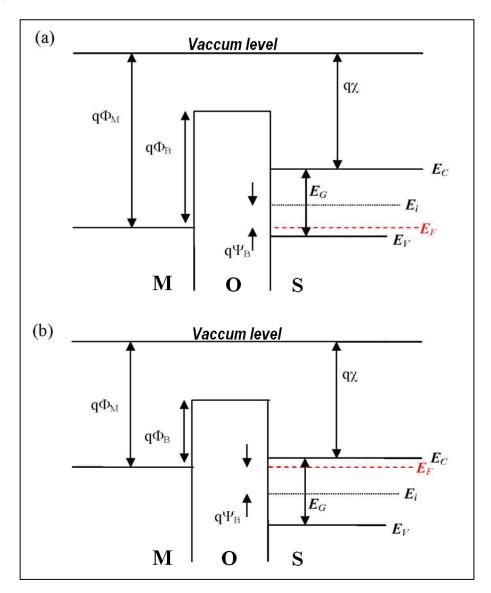

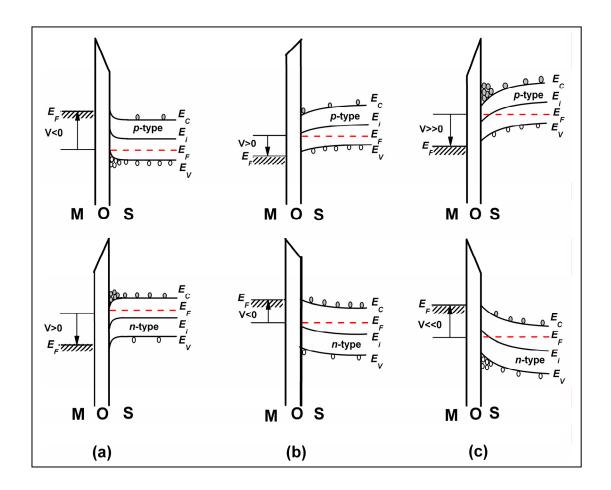

**Fig. 1.9:** The energy band diagrams of an ideal (no oxide charges, perfect insulator, and uniformly doped substrate, V=0) MOS device with a (a) p-type semiconductor and (b) n-type semiconductor.

**Fig. 1.10:** Energy-band diagrams for ideal MOS capacitors under different bias, for the conditions of: (a) accumulation, (b) depletion, and (c) inversion. Top/bottom figures are for p-type /n-type semiconductor substrates.

#### 1.5.4 Qualitative Description

In the scenario presented, the substrate is at ground and the bias is applied to the metal gate. In this situation, the semiconductor Fermi level,  $E_{Fs}$  is at ground potential, and the metal gate Fermi level,  $E_{Fm}$ , can be considered as a "handle" that moves up for negative applied bias and down for a positive applied bias. Another important parameter to discuss is the metal-semiconductor work function,  $\Phi_{ms}$ . The work function of any materials is in units of electron

volts (eV) and is defined as the distance from the Fermi level to the vacuum level for a given material (Fig. 1.9). The metal-semiconductor work function is the difference of the metal work function ( $\Phi_m$ ) from that of the semiconductor ( $\Phi_s$ ). Thus,

$$\Phi_{ms} = \Phi_m - \Phi_s \tag{1.5}$$

### 1.5.5 Flatband

The flatband voltage is the voltage required to make the bands horizontal (i.e., with no band bending) as shown in Fig. 1.9 (a) and (b). Using the assumption that no charges are present in the oxide, the flatband voltage can be positive or negative depending on the value of  $\Phi_m$  relative to  $\Phi_s$ , as demonstrated in Fig. 1.11(c).

### 1.5.6 Accumulation

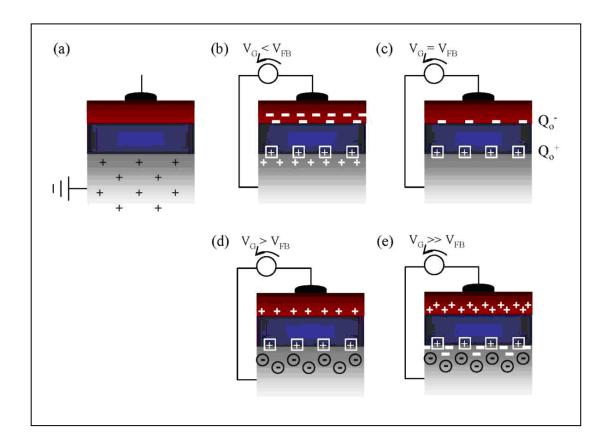

For both p/n-type MOS structures, accumulation occurs when a negative/positive bias is applied to the gate. The negative charges on the gate attract holes to the high- $\kappa$ /substrate (e.g. Dy<sub>2</sub>O<sub>3</sub>/p-Ge or CeO<sub>2</sub>/n-Ge) interface to form an accumulation layer (see Fig. 1.11(b)).

The band structure also undergoes a change from the previous static bias condition to the Figure 1.10(a) for both p/n-type substrates. When the negative/positive bias is applied to the gate, the Fermi level moves up/down relative to the grounded Fermi level in the substrate creating the band bending shown.

Fig. 1.11 (a)-(e): The metal-oxide semiconductor capacitor (MOSCAP) in (a) standby [no bias], (b) accumulation  $[V_g < V_{FB}]$ , (c) flatband  $[V_g = V_{FB}]$ , (d) depletion  $[V_g > V_{FB}]$ , and (e) inversion  $[V_g > V_{FB}]$ .

## 1.5.7 Depletion

As the bias increases from a negative/positive accumulation bias, holes/electron begin to leave the high- $\kappa$ /substrate (e.g. Dy<sub>2</sub>O<sub>3</sub>/Ge or CeO<sub>2</sub>/Ge) interface until the flatband condition is reached. Continuing to increase the bias begins to deplete holes/electrons at the interface as well as a certain distance into the p/n-type substrate forming a depletion region shown in Fig. 1.11(d).

The band structure also undergoes a change from a previous static bias condition to Figure 1.10(b) for both p/n-type substrates. When the increasing bias is applied to the gate the Fermi level moves downward/upward relative to the grounded Fermi level in the substrate creating the band bending shown.

#### 1.5.8 Inversion

As the bias continues to increase from a depletion bias, assuming sufficient inversion charge is established (which could take some time), a maximum depletion width is established, and then, electrons/holes begin to move towards the high- $\kappa$ /substrates (e.g. Dy<sub>2</sub>O<sub>3</sub>/p-Ge or CeO<sub>2</sub>/n-Ge) interface to form an inversion layer as shown in Fig. 1.11(e).

The band structure also undergoes a change as shown Figure 1.10(c) for p/n-type substrates. When the increasing bias is applied to the gate, the Fermi level continues to move downward/upward relative to the grounded Fermi level in the substrate creating the band bending shown.

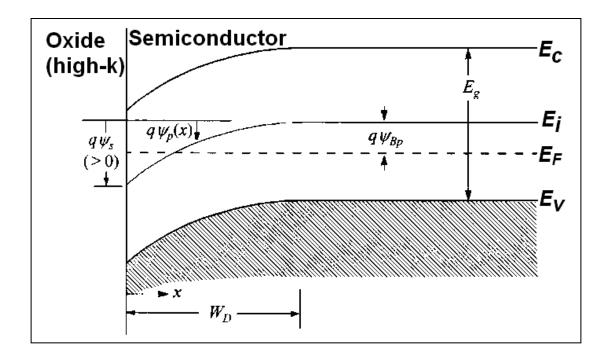

### 1.5.9 Surface Space-Charge Region

In this section we derive the relations between the surface potential, space charge, and electric field. These relations are then used to derive the capacitance-voltage characteristics of the ideal MOS structure in the following section.

Fig. 1.12: Energy-band diagram at the surface of a p-type semiconductor. The potential energy  $q\Psi_p$  is measured with respect to the intrinsic Fermi level  $E_i$  in the bulk, while  $W_D$  is the depletion width. The surface potential  $\Psi_S$  is positive as shown. Accumulation occurs when  $\Psi_S < 0$ . Depletion occurs when  $\Psi_{Bp} > \Psi_S > 0$ . Inversion occurs when  $\Psi_S > \Psi_{Bp}$ .

Figure 1.12 shows a more detailed band diagram at the surface of a p-type semiconductor. The potential  $\Psi_p(\mathbf{x})$  is defined as the potential  $E_i(\mathbf{x})/\mathbf{q}$  with respect to the bulk of the semiconductor,

$$\psi_p(x) = \frac{\left[E_i(x) - E_i(\infty)\right]}{q} \tag{1.6}$$

At the semiconductor surface,  $\Psi_p(\mathbf{x}) = \Psi_S$ , and  $\Psi_S$  is called the surface potential. The electron and hole concentrations as a function of  $\Psi_S$  are given by the following relations:

$$n_p(x) = n_{po} \exp\left(\frac{q \psi_p}{kT}\right) = n_{po} \exp(\beta \psi_p)$$

(1.7)

$$p_{p}(x) = p_{po} \exp\left(\frac{-q\psi_{p}}{kT}\right) = p_{po} \exp(-\beta\psi_{p})$$

(1.8)

where  $\Psi_p$  is positive when the band is bent downward (as shown in Fig. 1.12),  $n_{po}$  and  $p_{po}$  are the equilibrium densities of electrons and holes, respectively, in the bulk of the semiconductor, and  $\beta = q/kT$ .

From previous discussions and with the help of the above equations (1.5, 1.6, 1.7, and 1.8), the following regions of surface potential can be distinguished:

$\Psi_S < 0$  Accumulation of holes (band bending upward)

$\Psi_S = 0$  Flat-band condition.

$\Psi_{Bp} > \Psi_{S} > 0$  Depletion of holes (band bending downward)

$\Psi_S = \Psi_{Bp}$  Fermi-level at midgap,  $E_F = E_i(0)$ ,  $n_p(0) = p_p(0) = n_i$

$2\Psi_{Bp} > \Psi_{S} > \Psi_{Bp}$  Weak inversion [electron enhancement,  $N_A > n_p(0) > p_p(0)$ ]

$\Psi_S > 2\Psi_{Bp}$  Strong inversion [electron enhancement,  $n_p(0) > N_A$ ]

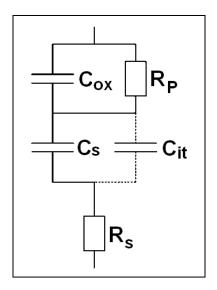

### 1.6 Capacitance-Voltage (C-V) characteristic

The Capacitance-Voltage behavior of a MOS device can be described using the equivalent circuit shown in Fig. 1.13 [39] where  $C_{OX}$  is the oxide capacitance,  $C_{S}$  the substrate capacitance,  $C_{it}$  the interface state capacitance,  $R_{S}$  the series resistance and  $1/R_{P}$  the parallel conductance.

**Fig. 1.13:** Equivalent circuit of an MOS structure including the oxide capacitance  $(C_{OX})$ , the substrate capacitance  $(C_S)$ , interface state capacitance  $(C_{it})$ , series resistance  $(R_S)$  and parallel conductance  $(1/R_P)$ .

The capacitance of a MOS capacitor is defined as

$$C = \frac{dQ_g}{dV_g} \tag{1.9}$$

Based on charge neutrality  $Q_g = -(Q_S + Q_{it})$  where  $Q_S$ , the substrate charge, and  $Q_{it}$ , the trapped interface charge. This assumes no charge trapping in the dielectric. The gate voltage is partially dropped across the dielectric and partially across the semiconductor substrate. This gives

$$V_{g} = V_{FB} + V_{OX} + \phi_{S}, \tag{1.10}$$

where  $V_{FB}$  is the flatband voltage,  $V_{OX}$  the voltage drop across the oxide and  $\phi_S$  the Ge surface potential allowing Eq. 1.1 to be written as

$$C = \frac{dQ_S + dQ_{it}}{dV_{OY} + d\phi_S},\tag{1.11}$$

Depending on the Ge surface potential either majority, minority or depletion charge is contributing to the substrate charge. The total gate capacitance can now be written as

$$C = \frac{1}{\frac{1}{C_{OX}} + \frac{1}{C_S + C_{ii}}}$$

(1.12)

The low – frequency substrate capacitance is given by

$$C_{S,lf} = \hat{U}_S \frac{\varepsilon_S \varepsilon_0}{2L_{Di}} \frac{\left[e^{U_F} \left(1 - e^{-U_S}\right) + e^{-U_F} \left(e^{U_S} - 1\right)\right]}{F(U_S, U_F)}$$

(1.13)

where the dimensionless surface electric field  $F(U_S, U_F)$  is defined by

$$F(U_S, U_F) = \sqrt{e^{U_F} (e^{-U_S} + U_S - 1) + e^{-U_F} (e^{U_S} - U_S - 1)}$$

(1.14)

$U_S$  and  $U_F$  are normalized potentials, defined as  $U_S = q\phi_S/kT$ , and  $U_F = q\phi_F/kT$ . The Fermi potential is calculated by,  $\phi_F = (kT/q)\ln(N_A/n_i)$ , where  $N_A$  is the acceptor concentration and  $n_i$  the intrinsic carrier concentration in the Ge substrate. The symbol  $\hat{U}_S$  stands for the sign of the surface potential and is given by

$$\hat{U}_S = \frac{|U_S|}{U_S} \tag{1.15}$$

where  $\hat{U}_S = 1$  for  $U_S > 0$  and  $\hat{U}_S = -1$  for  $U_S < 0$ . The extrinsic Debye length  $L_{Di}$  is

$$L_{Di} = \sqrt{\frac{\varepsilon_{s}\varepsilon_{0}kT}{2q^{2}n_{i}}}$$

(1.16)

The high-frequency C-V curve results when the minority carriers in the inversion charge are unable to follow the ac voltage. The majority carriers at the semiconductor edge are able to follow to the ac signal thereby exposing more or less ionized dopants atoms. The high – frequency semiconductor capacitance in inversion is [40]

$$C_{S,hf} = \hat{U}_S \frac{\varepsilon_S \varepsilon_0}{2L_{Di}} \frac{\left[e^{U_F} \left(1 - e^{-U_S}\right) + e^{-U_F} \left(e^{U_S} - 1\right)\right]/(1 + \delta)}{F(U_S, U_F)}, \tag{1.17}$$

with  $\delta$  given by

$$\delta = \frac{\left(e^{U_S} - U_S - 1\right) / F(U_S, U_F)}{\int_0^{U_S} \frac{e^{U_F} \left(1 - e^{-U}\right) \left(e^U - U - 1\right)}{2[F(U_S, U_F)]^3} dU},$$

(1.18)

## 1.6.1 High-low Capacitance-Voltage (C-V) characteristic curves

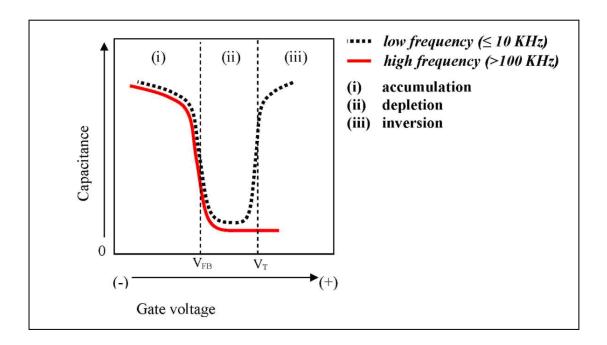

With a sufficiently negative and positive voltage, an accumulation and inversion layer is obtained in the MOS structure. Figure 1.12 shows the characteristic low-frequency and high-frequency trends of the capacitance as a function of applied gate voltage. At high frequencies, the minority carrier is unable to respond, and the majority carriers are able to respond in negative gate bias, or accumulation.

Fig. 1.14: The three operating regions of the device shown for a capacitance-voltage (CV) measurement of an MOS device at a low measurement frequency (<10 kHz, black-dashed line) and a high measurement frequency (>100 kHz, red line).

# 1.6.2 Frequency dispersion of C-V characteristics

## 1.6.2.1 Frequency dispersion at accumulation

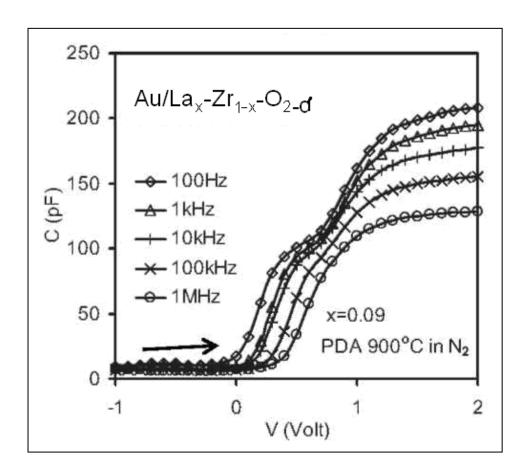

There are several mechanisms which may cause the dispersion of the capacitance with frequency observed (Fig. 1.15) at accumulation: (i) series resistances [41], (ii) parasitic effects in cluding back contact imperfection [42-43],(iii) a  $\kappa$ -value dependence on frequency of the interfacial dielectric layer [44]. To obtain the intrinsic properties and permittivity of the REOs dielectric from the C-V measurements, the

Fig. 1.15: C-V results at different frequencies from the annealed sample  $Au/La_x$ - $Zr_{1-x}$ - $O_{2-\delta}/p$ -Si for x=0.09. Significant frequency dispersion at accumulation was observed. After Ref. [45]

above mentioned effects must be eliminated. To reduce the effects of series resistance, back contacts (e.g. In-Ga alloy) can be deposited over a large area of the substrate wafer, which suppresses the effect of series resistances and back contact imperfections [42]. Cables and connections must be kept short to further minimize parasitic effects [43] as well.

### 1.6.2.2 Frequency dispersion at inversion

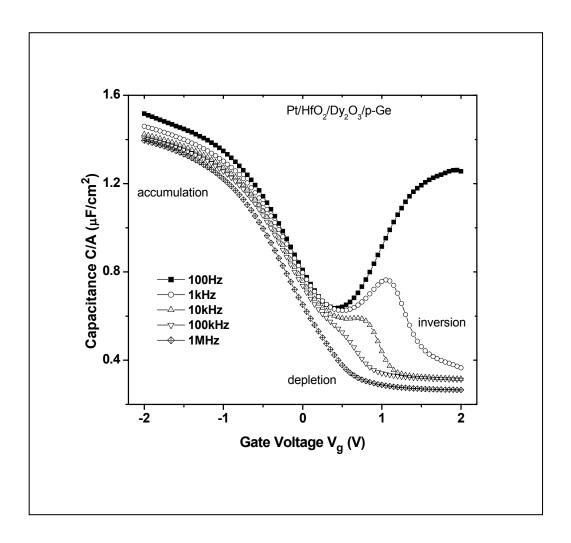

Germanium MOSFETs with high- $\kappa$  dielectric gates could be good alternatives for future high performance logic devices due to the (low field) high carrier mobility [46]. The low frequency behaviour of the high frequency capacitance-voltage (C-V) curves (see Fig. 1.16), or more specifically, the observation of a high ac inversion

**Fig. 1.16:** Room temperature C-V characteristics of an n type  $Pt/HfO_2/n$ -Ge MOS measured at different frequencies from 20 Hz to 1 MHz. Large frequency dispersion is observed at inversion (negative Vg). The transition frequency  $f_m$ , 6 kHz defined as the frequency at which the inversion capacitance is midway between low and high values, marks the transition from a low to high frequency behavior. After Ref. [48]

capacitance [47] (close to the oxide capacitance value  $C_{ox}$ ) at high frequencies (in kHz range) which is not expected based on the experience we have with device quality Si. This behaviour is usually attributed to contamination [47, 49] due to poor quality of bulk Ge starting material or due to insufficient surface passivation which creates high density of interface traps or mid-gap bulk semiconductor traps through metal diffusion from the high- $\kappa$  over layer. These traps are considered to mediate the creation of electron-hole pairs in the depletion to provide the necessary seed of minority carriers which are necessary to built the inversion layer and give the high value of capacitance. The density of minority carriers in Ge though is expected to be higher compared to Si due to the lower energy gap (or higher intrinsic carrier concentration  $n_i$ ). This could induce low frequency behaviour in Ge at high frequencies. As a matter of fact, Nicollian and Brews [41], had already predicted long before about this behaviour.  $f_m$  defined [41] as the frequency at which the capacitance in inversion is midway between high  $C_{inv}$  (20 Hz) and low  $C_{HF}$  values, marking the transition from low frequency to high frequency behavior.

Due to the short minority carriers' response time in Ge, an inversion layer is formed fast in response to an external ac signal at the gate, so that a high capacitance, equal to  $C_{ox}$  is formed even at high frequencies i.e., (1 kHz).

### 1.7 Interface state characterization

#### 1.7. 1 Introduction

Next to the leakage current, the single most important metric for determining the usefulness of new gate dielectrics is the interface trap state density ( $D_{it}$ ). The presence of interface states in a MOS device leads to several undesirable behaviors. First, the presence of any charge, whether it be at the interface or in the oxide itself leads to a shift in the capacitance voltage

(*C-V*) characteristics of the device. In a MOSFET, this directly translates to a change in threshold voltage. Second, since interface traps fill and empty with some characteristic time constant, there will be dispersion in the capacitance of the device as a function of frequency. Third, a large amount of trapped charge at the interface will degrade the channel mobility of a MOSFET via coulomb scattering of carriers. Finally, the sub-threshold current swing in a MOSFET is adversely affected by interface trap states. As a matter of fact, interface states are strongly correlated to the quality of the high- $\kappa$  single dielectrics and/or gate stacks with semiconductor interlayer, and have been used as one of the primary parameters to characterize and monitor gate dielectric reliability.

### 1.7.2 Extraction of interface trap density $(D_{it})$

### **1.7.2.1** Theory

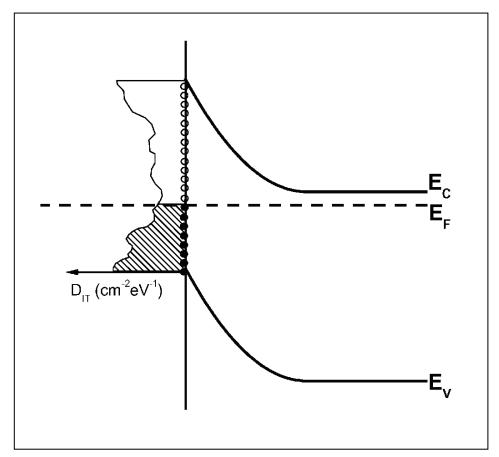

The first method for determining interface state density is the high-frequency capacitance method, also known as the Terman method, and in this method, the only measurement necessary is the high frequency (typically on the order of 1 MHz) capacitance versus voltage (C-V) curve. Even though interface traps cannot fill and empty on the time scales used to measure the capacitance, they can respond to the quasi-static bias sweep used to produce the C-V curve. Figure 1.17 illustrates that as the Fermi level crosses through the interface state distribution at a semiconductor surface; a sheet charge at the surface is created that is directly proportional to either the number of empty interface states for donor-like traps or filled states for acceptor-like traps. Since this sheet charge will depend on the position of the Fermi level at the interface, it will depend on the surface potential  $\Psi s$ , and thus the applied gate voltage. This voltage-dependent charge layer can have a pronounced effect on the C-V characteristics even though the traps at the surface are not filling and emptying in phase with the ac signal.

What the trap states will do is to change the gate voltage for which a given  $\Psi s$  is obtained. Donor-like states are defined as positively charged when empty and acceptor-like states are defined as negatively charged when filled.

Figure 1.17: Schematic of an insulator-semiconductor interface with interface states.

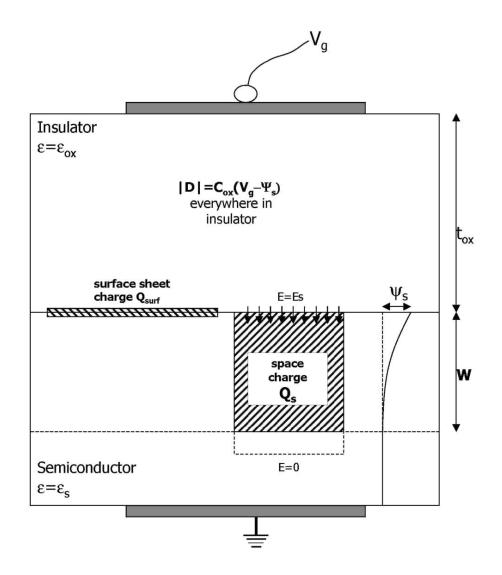

At an insulator-semiconductor interface with dielectric constants,  $\varepsilon_{ox}$  and  $\varepsilon_{S}$ , and with a sheet charge  $\delta Q_{sheet}$  present at the interface, one of Maxwell's equations,

$$\nabla \bullet D = \rho \tag{1.19}$$

leads to the boundary condition

$$\varepsilon_{ox} E_{ox}^{\perp} - \varepsilon_{S} E_{S}^{\perp} = -Q_{sheet} \tag{1.20}$$

where the  $\perp$  superscript implies the component of the electric field perpendicular to the interface. If  $\Psi s$  is the potential at the semiconductor surface then boundary condition (1.20) becomes

$$C_{ox}(V_g - \Psi_S) - \varepsilon_S E_S^{\perp} = -Q_{sheet}$$

(1.21)

where  $C_{ox} = \varepsilon_{ox}/t_{ox}$  is the oxide capacitance,  $V_g$  is the applied gate bias,  $Q_{sheet}$  is any sheet charge located at the insulator-semiconductor interface, and  $Q_S$  is the depletion/inversion charge in the semiconductor (Fig.1.18). Now we apply Gauss' law to an area just below the interface, from the semiconductor surface to beyond the depletion layer. The electric field entering the Gaussian box at the top is just  $E_S^{\perp}$ . Since the other side of the box is outside of the depletion region, the field leaving the box on the bottom is just zero. Because of symmetry in the direction parallel to the interface, there are no field lines leaving the sides of the box. Thus, Gauss' law gives

$$E_S^{\perp} = \frac{Q_S(\Phi_S)}{\varepsilon_S},\tag{1.22}$$

where the  $\Phi$ s is included in order to emphasize the point that the semiconductor space charge is a function of the band bending. Now plugging (1.20) back into Eq. (1.19) we have,

$$C_{ox}(V_g - \Psi_S) = -Q_{sheet} - Q_S(\Phi_S)$$

(1.23)

In the case of a sheet charge generated by interface states,  $Q_{sheet}$  is also a function of  $\Psi_s$  as shown in Fig. 1.18. If  $Q_{sheet}$  is replaced by  $Q_{it}(\Psi_s)$ ,  $V_g$  can be solved for, then differentiated with respect to  $\Psi_s$  to obtain

$$\frac{dV_g}{d\Psi_S} = 1 - \frac{1}{C_{ox}} \left( \frac{dQ_{it}}{d\Psi_S} + \frac{dQ_S}{d\Psi_S} \right)$$

(1.24)

Fig. 1.18: Schematic of the important charges, fields and potentials at the insulator (oxide) semiconductor interface.

The derivatives of the interface state charge and the semiconductor charge can be rewritten as capacitances,  $C_{it}$  and  $C_s$ , giving

$$C_{it} = C_{ox} \left( \frac{dV_g}{d\Psi_S} - 1 \right) - C_S(\Psi_S)$$

(1.25)

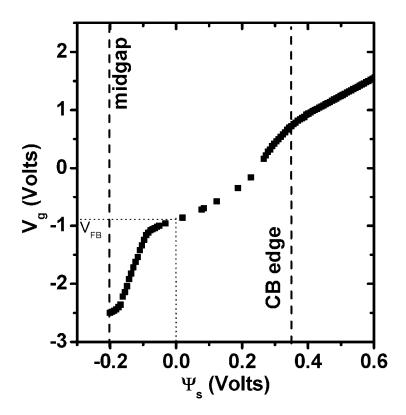

**Fig. 1.19:** Example of a measured curve of  $V_g$  vs.  $\Psi$ s. The derivative of this curve is used to compute the interface state density in the Terman method. This curve is also used to relate the position of the Fermi level within the germanium bandgap to the applied gate bias in both the Terman method and the conductance method.

For an interface state density that is slowly varying throughout the energy gap relative to kT the interface state density can be approximated simply as  $D_{ii} = qC_{ii}$  [41]. The important parameter to determine for this calculation is  $dV_g/d\Psi_s$ , which is an indication of how the band bending changes with applied gate voltage. The Terman method calculates this parameter as a function of  $\Psi s$  by comparing an ideal theoretical C-V curve as a function of  $\Psi s$  with the measured C-V curve. For each value of capacitance at a given  $\Psi s$  in the theoretical curve, there is the corresponding value of capacitance at a given  $V_g$  in the measured curve. Thus it is possible to construct a curve of  $V_g$  vs.  $\Psi s$  such as the one shown in Fig. 1.19.

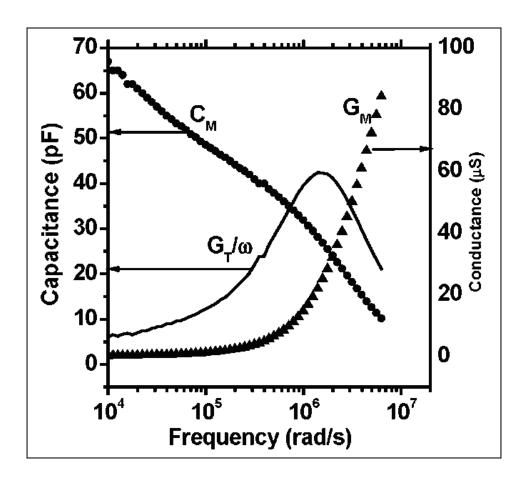

In addition, conductance method [50] is widely being used for extracting density of interface states for high mobility Ge based MOS devices. Conductance can be written simply as a function of  $G_m$ ,  $C_m$ , and  $C_{ox}$ , and:

$$G_{t}(\omega) = \frac{\omega^{2} C_{ox} G_{m}}{G_{m}^{2} + \omega^{2} (C_{m}^{2} - C_{ox}^{2})},$$

(1.26)

where  $C_{ox}$  can be measured directly in strong accumulation *i.e.*

$$C_{ox} = C_{ma}[1 + (G_{ma}/\omega C_{ma})],$$

(1.27)

is oxide capacitance and  $C_{ma}$  and  $G_{ma}$  are capacitance and conductance in accumulation, while  $R_S = G_{ma}/[G_{ma}^2 + (\omega C_{ma})^2]$ ,  $\omega$  the angular frequency,  $C_m$  and  $G_m$  are measured capacitance and conductance respectively. A plot of  $G_{t}/\omega$  will be peaked as shown in Fig. 1.20. This peak can be thought of as occurring at a frequency for which the trap states are in "resonance" with the applied ac signal. At this frequency the highest possible numbers of traps are contributing to the conductance as described above. Thus the peak value of  $G_{t}/\omega$ , which we will denote as  $(G_{t}/\omega)_p$ , should be roughly proportional to the interface trap density. However, statistical variations in the nature of the charge distribution under the gate cause fluctuations in the band-bending at the semiconductor surface. This can smear out the peaks and reduce their magnitude. The standard deviation of these fluctuations,  $\sigma_s$ , is related to the width of peak in the  $G_{t}/\omega$  vs.  $\omega$  curve and can be calculated from the data [41].  $D_{tt}$  is calculated approximately from the magnitude of the peak of  $G_{t}/\omega$  curves at a given bias:

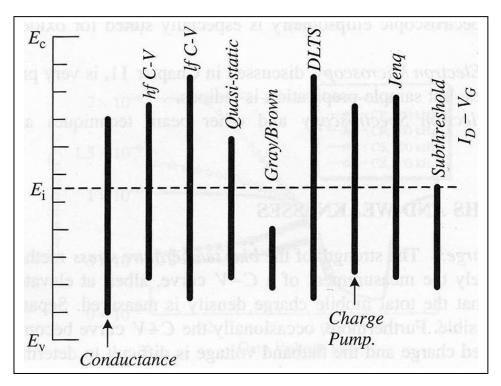

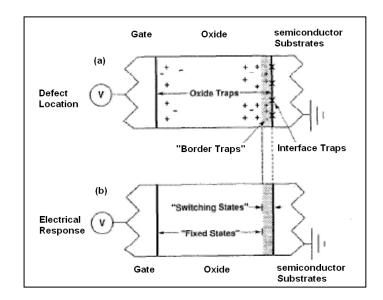

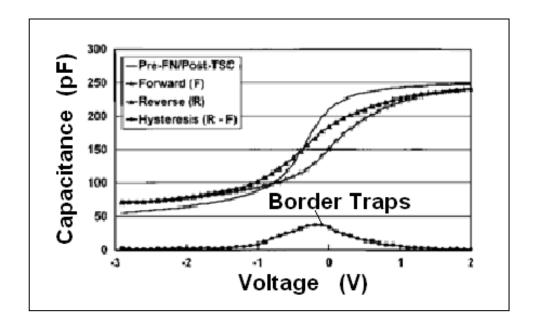

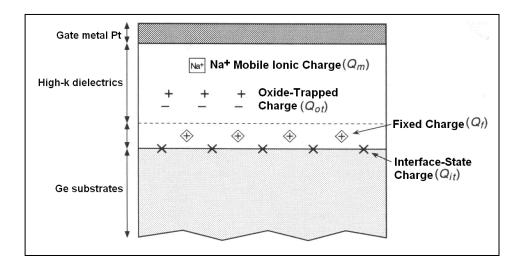

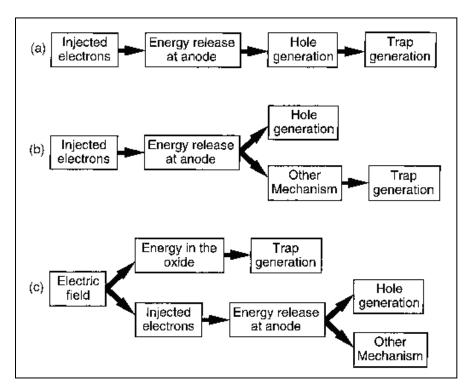

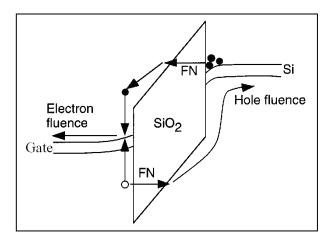

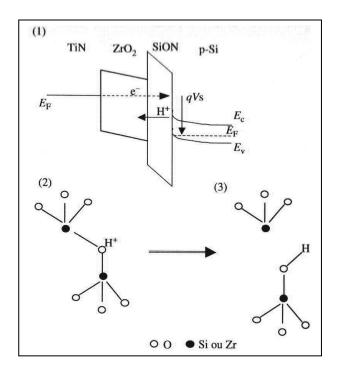

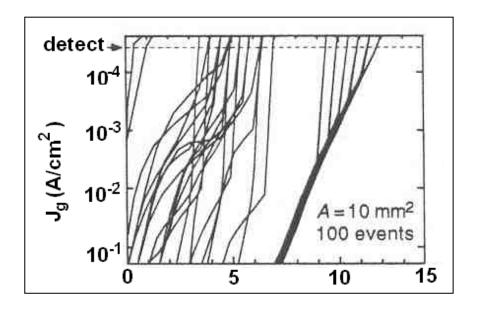

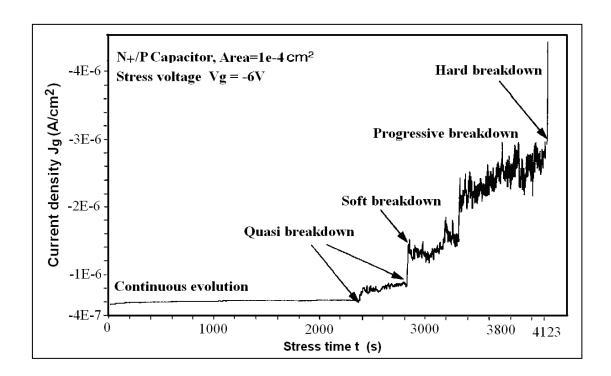

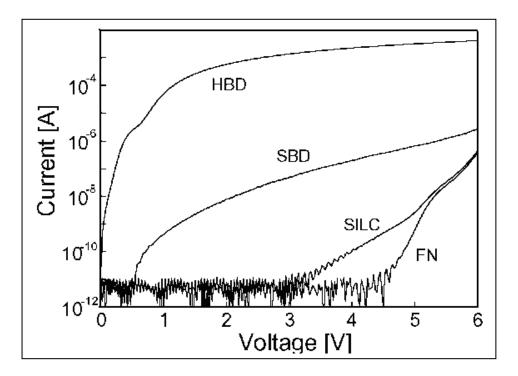

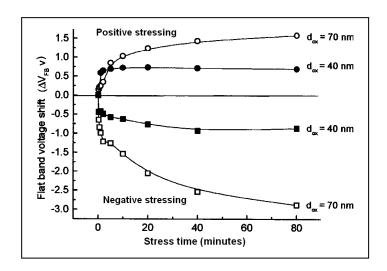

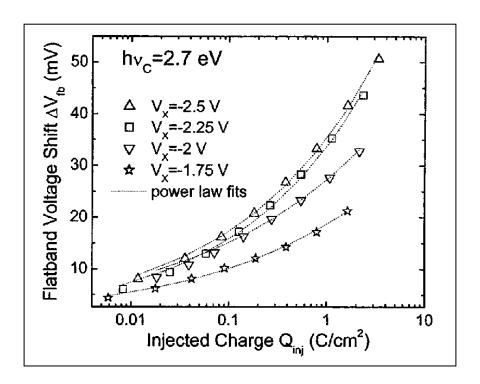

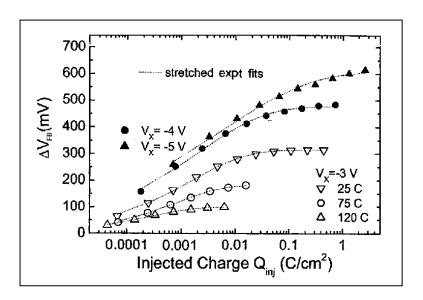

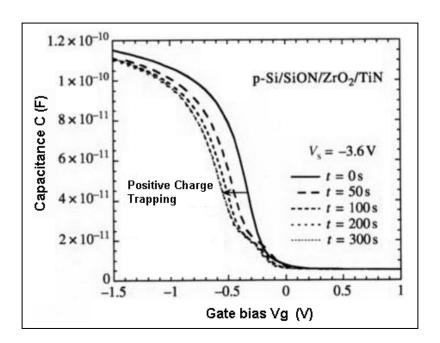

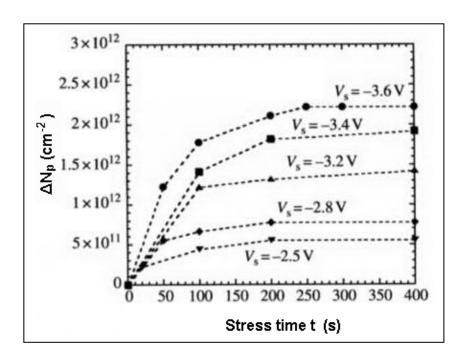

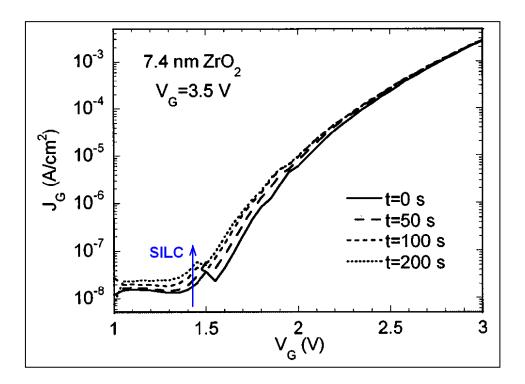

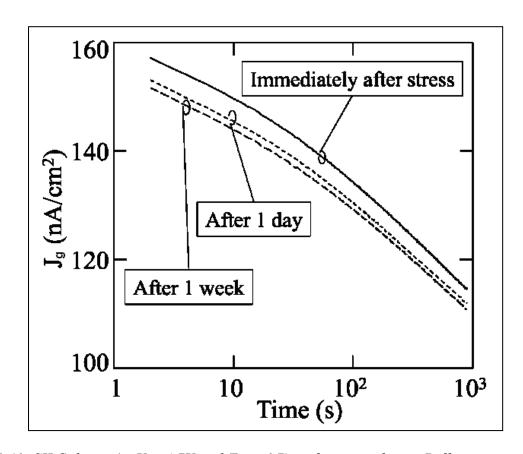

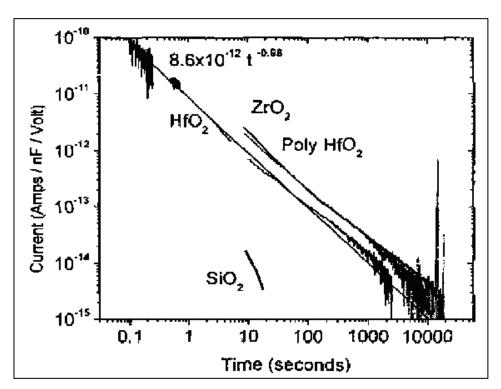

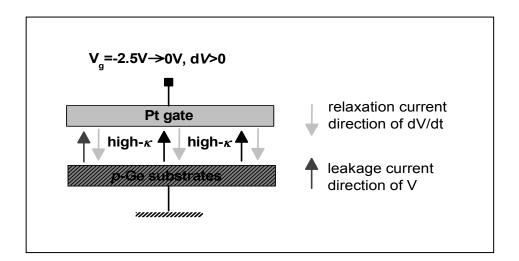

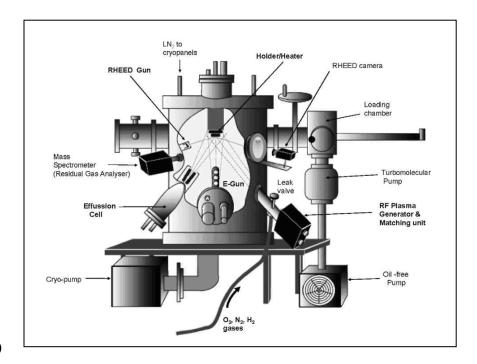

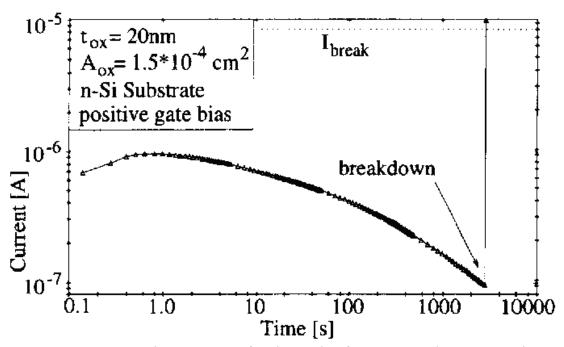

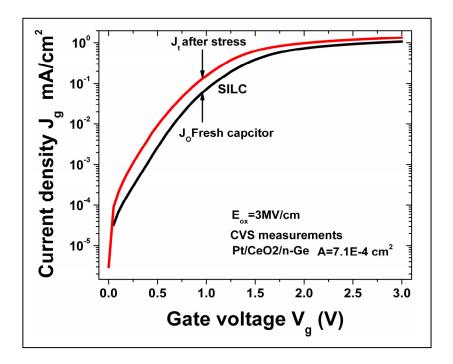

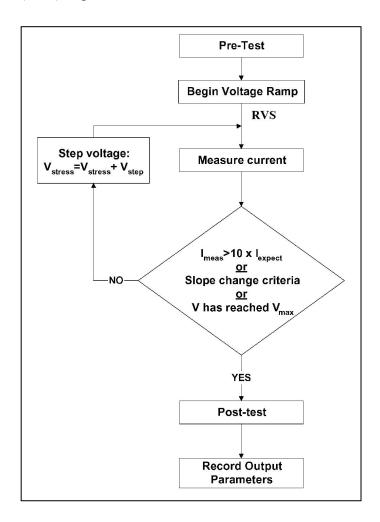

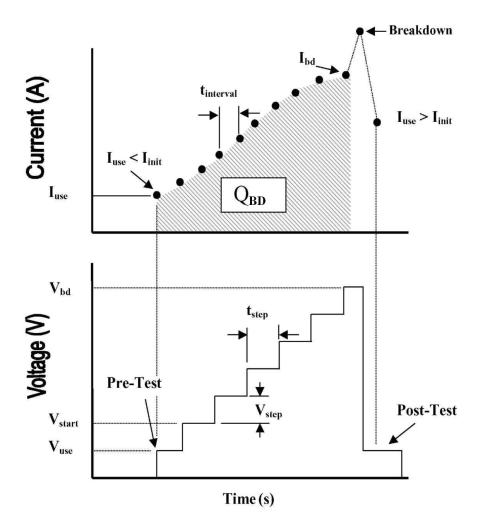

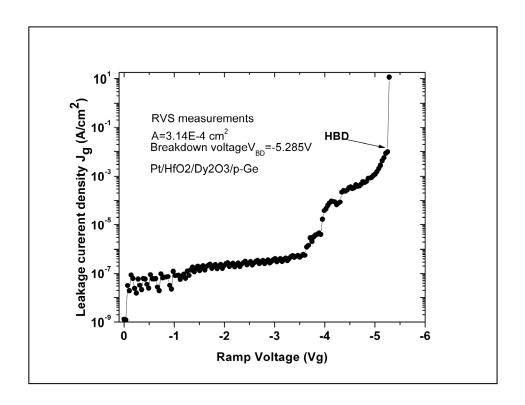

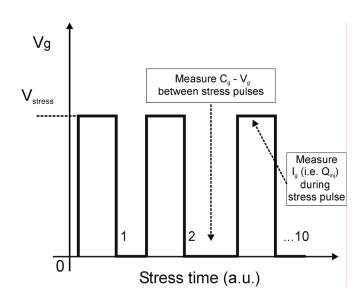

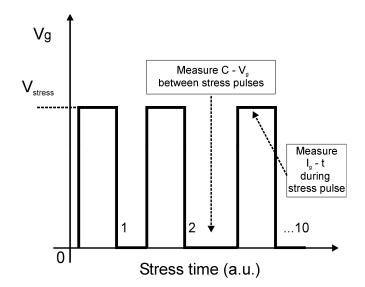

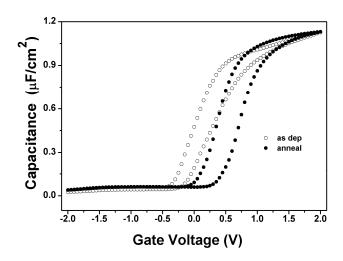

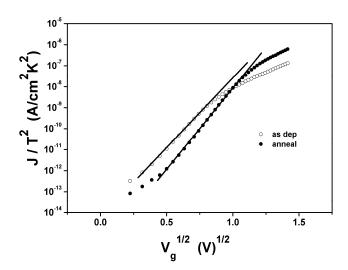

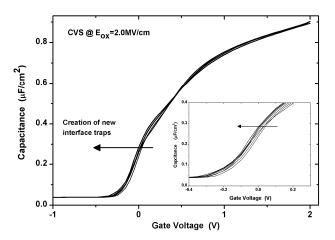

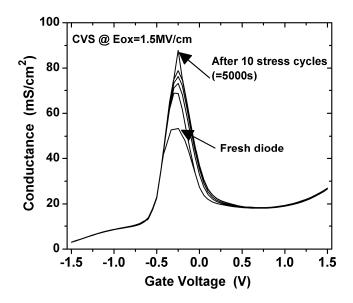

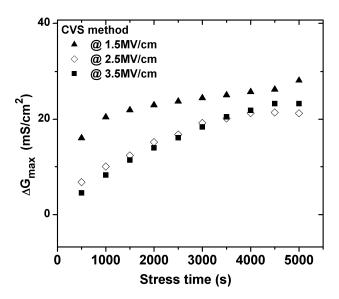

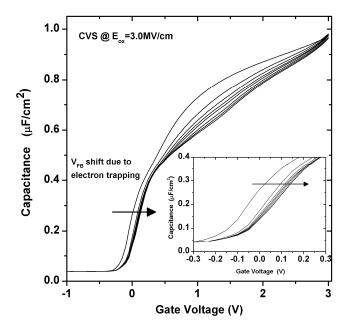

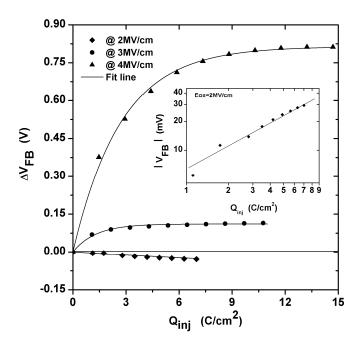

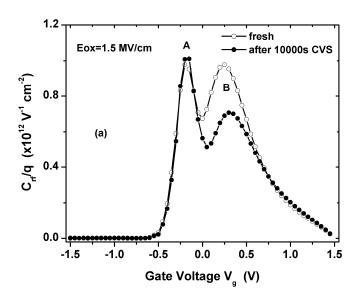

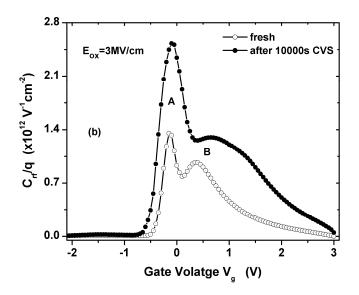

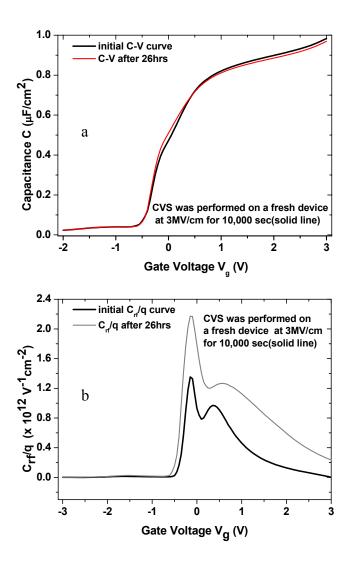

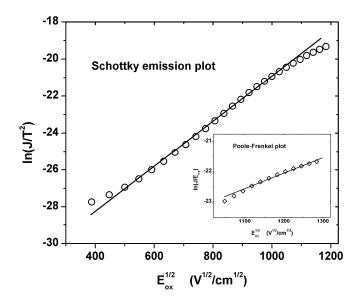

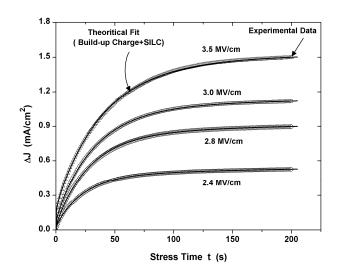

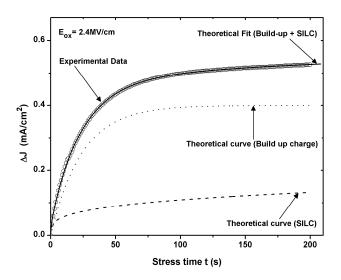

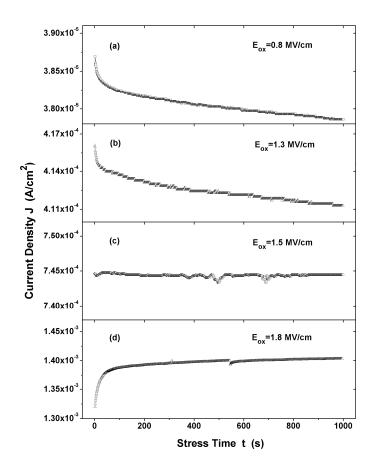

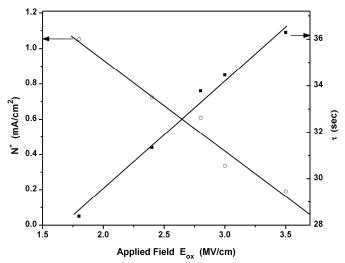

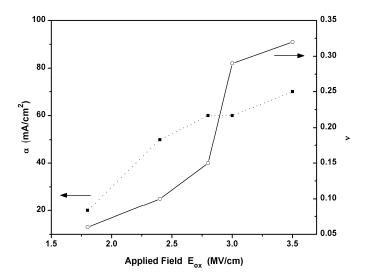

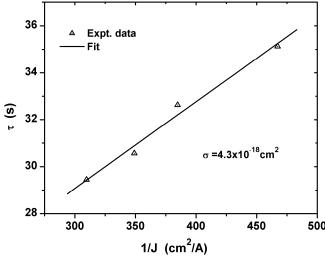

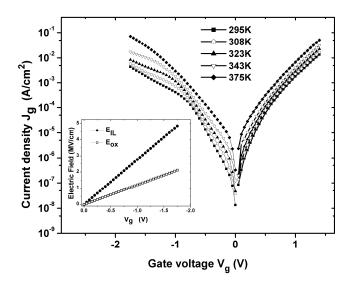

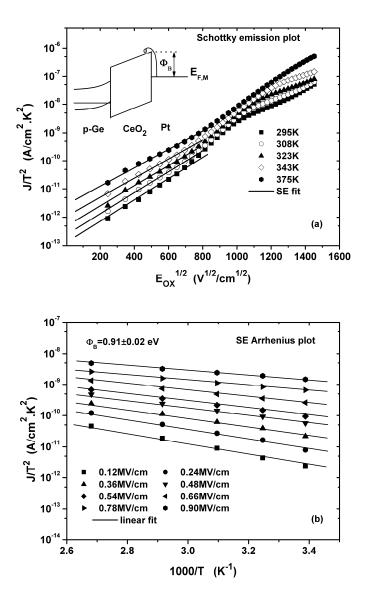

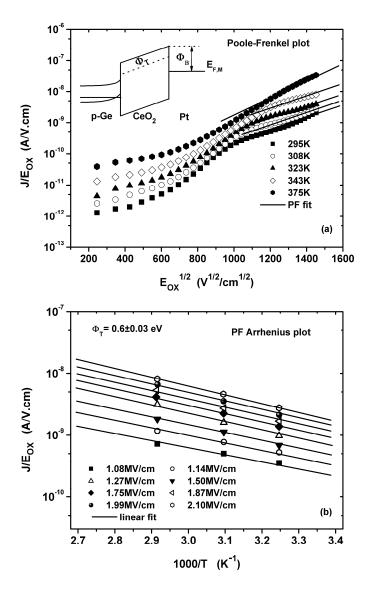

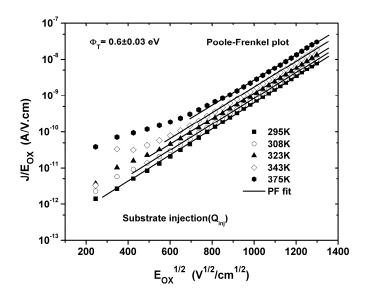

$$D_{it} \approx \frac{2.5}{q} \left(\frac{G_t}{\omega}\right)_p \tag{1.28}$$